Программируемые логические ИС (ПЛИС)

Еще недавно в распоряжении разработчика цифровых электронных устройств имелась лишь «жесткая» логика. Искусство проектирования заключалось в достижении поставленной цели с помощью минимального числа ИМС, способных выполнять лишь строго определенные функции. Устройство отлаживали и совершенствовали, перерезая печатные проводники и «навешивая» проволочные перемычки и дополнительные детали. Нередко ошибки, допущенные на этапе проектирования, удавалось исправить только ценой изготовления новой печатной платы.

Микропроцессоры ситуации почти не изменили, ведь каждый из них требует довольно сложной «обвязки» из обычных логических элементов. К тому же во многих случаях специализированные цифровые устройства решают задачу эффективнее универсальных микропроцессорных.

Революция началась с появлением ИМС ППЗУ и программируемых логических матриц (ПЛМ или PLD – programmable logical device). Пережигая с помощью програссатора предусмотренные в них плавкие перемычки, разработчик получил возможность реализовать в одной ИМС десяток почти любых логических функций. Типичными представителями однократно программируемых ППЗУ и ПЛМ – отечественные серии 556 и 1556. Но ИМС с лишней пережженной перемычкой приходилось выбрасывать.

Многократно программируемые ПЗУ с УФ стиранием, к сожалению, мало подходят для реализации логических функций из-за недостаточного быстродействия.

Некоторое распространение получили «заказные» ИМС на основе БМК (серии К1515 и К1520). БМК содержат сотни логических элементов и способен заменить несколько десятков ИМС малой и средней степени интеграции. Элементы соединяют прямо на кристалле по нужной заказчику схеме на последних этапах производственного цикла. Естественно, заказывать такие ИМС имеет смысл при потребности не менее нескольких сотен штук (nх100), а изменить что-либо в готовом приборе невозможно.

Дальнейшее развитие технологии ПЛМ и БМК привело к созданию программируемых логических интегральных схем (ПЛИС). Реализуемые ими функции можно многократно изменять, нередко для этого даже не нужно извлекать ИМС из устройства, в котором она работает.

Подобно БМК, кристалл ПЛИС содержит большое число однотипных логических элементов. Основное отличие в том, что соединяют элементы в нужном порядке с помощью электрически программируемых перемычек – ключей на МОП-транзисторах. А в каждом логическом элементе имеются переключатели (мультиплексоры), программируя которые, можно изменять выполняемые функции. Почти все внешние выводы ПЛИС универсальны. Любой из них может служить входом, выходом или быть двунаправленным. Некоторые выводы имеют дополнительные функции, например, служат для программирования конфигурации ИМС, что, однако, не исключает их использования в качестве обычных входов или выходов.

По внутренней конфигурации и способу запоминания конфигурации ПЛИС фирмы Xilinx можно разделить на два вида:

- FPGA (field programmable gate array) – матрица вентилей, программируемых электрическим полем (серии ХС2000, ХС3000, ХС4000, ХС5200, ХС6000 и SPARTAN ;

- CPLD (complex programmable logic device) – сложная программируемая логическая матрица (ХС7000 и ХС9500).

Подобно ОЗУ, FPGA сохраняют заданную конфигурацию только при включенном питании и «забывают» ее после выключения. Каждый раз, включив питание, такую ПЛИС необходимо программировать заново. Программу обычно хранят в установленном на одной плате с ПЛИС загрузочном ПЗУ. Процедура перезаписи выполняется автоматически, после чего ПЛИС переходит в рабочий режим.

В одном ПЗУ допускается хранить информацию для нескольких ПЛИС. Одна из них служит ведущей (master) и закончив собственную загрузку, управляет записью данных в ведомые (slave) ИМС. Назначение ведущей или ведомой никак не влияет на логические функции, выполняемые ПЛИС после загрузки.

Микросхемы CPLD сохраняют конфигурацию независимо от наличия питающего напряжения. В микросхемы ХС7000 конфигурацию заносят с помощью программатора, а стирают УФ излучением. Такие ПЛИС устанавливают, как правило, в уже отлаженные устройства. Для отладки новых устройств они неудобны из-за длительной (до часа) процедуры стирания (причем всей информации).

Микросхемы ХС9500, выполненные по технологии FLASH, можно неоднократно программировать не извлекая из устройства, в которое они установлены. Для этого в них предусмотрен специальный порт (JTAG). Чтобы записать или внести в нее изменения, выводы этого порта через несколько буферных микросхем соединяют кабелем с портом LPT персонального компьютера. Через него же компьютер может получить информацию о логических уровнях на всех выводах ПЛИС и контрольных точках внутри нее.

Возможность организовать такой порт предусмотрена и в ПЛИС структуры FPGA последних серий.

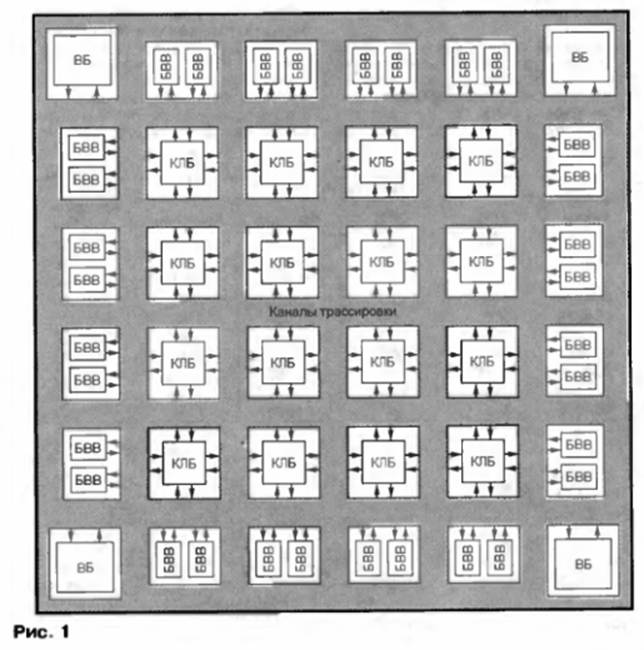

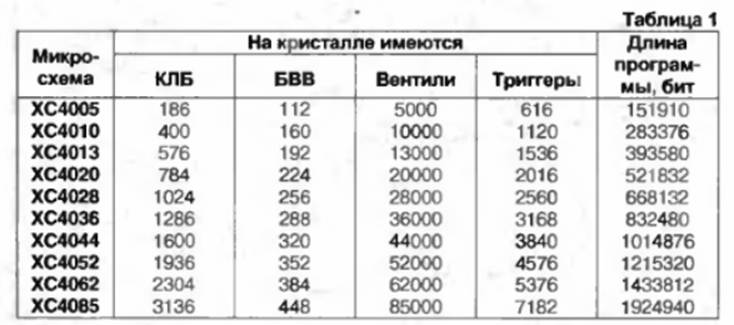

На рис.1 схематично показана структура кристалла микросхемы FPGA. Ее центральную часть занимает матрица конфигурируемых логических блоков (КЛБ), а по периметру находятся блоки ввода/вывода (БВВ), соединенные с контактными площадками. Представление о сложности современных ПЛИС дает табл.1., где приведены сведения о числе КЛБ и БВВ, имеющихся в серии ХС4000. Вентили и триггеры в данном случае не самостоятельные элементы, а входят в состав указанных блоков. Каждый из БВВ способен быть входным или выходным.

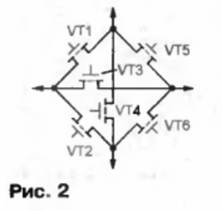

По углам кристалла расположены вспомогательные узлы. Свободную от логических элементов площадь занимают каналы трассировки, где проложено большое число проводников, на пересечении которых находятся программируемые ключи. Каждый ключ состоит из 6 МОП-транзисторов, соединенных как показано на рис.2.

Задавая открытое или закрытое состояние каждого из транзисторов, можно соединить КЛБ между собой и с БВВ нужным образом.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.