|

|

00 |

01 |

11 |

10 |

|

00 |

01 |

11 |

10 |

|

00 |

01 |

11 |

10 |

|

00 |

01 |

11 |

10 |

|

00 |

0 |

0 |

X |

1 |

00 |

0 |

1 |

X |

0 |

00 |

1 |

1 |

X |

1 |

00 |

1 |

1 |

X |

1 |

|

01 |

0 |

1 |

Х |

1 |

01 |

1 |

0 |

Х |

1 |

01 |

0 |

0 |

Х |

0 |

01 |

0 |

0 |

Х |

0 |

|

11 |

0 |

1 |

Х |

X |

11 |

1 |

0 |

Х |

X |

11 |

1 |

1 |

Х |

X |

11 |

0 |

0 |

Х |

X |

|

10 |

0 |

1 |

Х |

X |

10 |

1 |

0 |

Х |

X |

10 |

0 |

0 |

Х |

X |

10 |

1 |

1 |

Х |

X |

6

Структурная схема счётчика приведена в приложении 1.

6.Анализ структурной схемы.

При включении питания выходы счётчика устанавливаются в произвольное состояние. На входах загрузки и установки в начальное состояние присутствует напряжение логической единицы, а на входах предустановки и синхронизации – логического нуля, рис. 7.

-

На входе установки в начальное состояние появляется напряжение нуля, и

на выходах счётчика формируется двоично-десятичный код (1-1-1-1)

соответствующий цифре 9, так как на входах ![]() триггеров

всех разрядов присутствует логический нуль, а на входах

триггеров

всех разрядов присутствует логический нуль, а на входах ![]() логическая

единица. На входы предварительной установки подаётся цифра 3 в коде 6-3-1-1

(0-1-0-0) и разрешение загрузки

логическая

единица. На входы предварительной установки подаётся цифра 3 в коде 6-3-1-1

(0-1-0-0) и разрешение загрузки ![]() . Но из-за того, что

. Но из-за того, что ![]() предварительная установка не происходит.

Приходят импульсы синхронизации.

предварительная установка не происходит.

Приходят импульсы синхронизации.

-

![]() , загрузка данных предустановки - на

выходах счётчика формируется двоично-десятичный код Айкена соответствующий

цифре 3. Напряжение на входе разрешения загрузки принимает значение равное

логической единице, дальнейшие значения входов

, загрузка данных предустановки - на

выходах счётчика формируется двоично-десятичный код Айкена соответствующий

цифре 3. Напряжение на входе разрешения загрузки принимает значение равное

логической единице, дальнейшие значения входов ![]() ,

, ![]() ,

, ![]() ,

, ![]() значения не имеют.

значения не имеют.

-

Приходит отрицательный фронт синхронизирующего импульса ![]() и счётчик переключается в следующее

состояние – на выходах код цифры 2. Режим счёта.

и счётчик переключается в следующее

состояние – на выходах код цифры 2. Режим счёта.

-

После достижения нуля счётчик с приходом следующего отрицательного

фронта на вход ![]() , переходит в состояние 9 (код

1-1-1-1), а затем в 8, 7 и так далее, т. е. работает как обычный вычитающий

счётчик.

, переходит в состояние 9 (код

1-1-1-1), а затем в 8, 7 и так далее, т. е. работает как обычный вычитающий

счётчик.

7. Разработка электрической схемы и описание её работы.

Электрические схемы логических элементов построим на основе схем базовых ЛЭ, изменяя их в зависимости то требований предъявляемых к ним. Если ЛЭ подключен ко входу проектируемого устройства, то необходимо учесть, что он будет работать на длинную линию и сохранить антизвонные диоды. В том случае, если ЛЭ стоит на выходе счётчика, следует обеспечить хорошую нагрузочную способность и сохранить сложный инвертор с каскадом Дарлингтона. В элементах внутренней структуры можно исключить и антизвонные диоды, и каскад Дарлингтона с целью уменьшения потребляемой мощности, задержки сигнала и занимаемой площади кристалла.

Электрические схемы логических элементов и используемых в счётчике приведены в приложении 3.

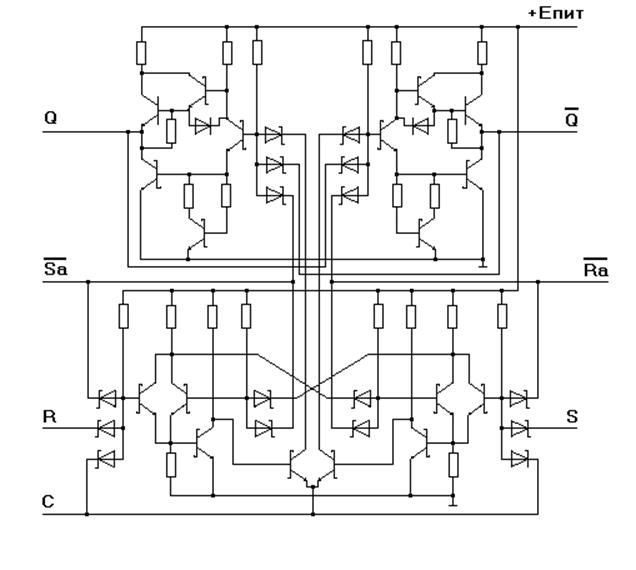

На рис. 8 изображена электрическая схема триггера используемого в счётчике.

Рис. 8. Электрическая схема RS-триггера.

8.Заключение.

В заключение следует отметить, что недостатками спроектированного счётчика является отсутствие выхода переноса в старший разряд для каскадирования и асинхронный вариант предустановки. Так же на вход синхронизации следовало подключить к счётчику буферный элемент с гистерезисом. Выход переноса можно организовать вне микросхемы счётчика, подключив к его выходам КУ.

9. Литература.

1. Алексенко А. Г., Шагурин И. И. Микросхемотехника. – М.: Радио и связь, 1982.

2. Белоус А. И., Пономарь В. Н., Силин А. В. Схемотехника биполярных микросхем для высокопроизводительных систем обработки информации. – Мн.: Полифакт, 1998.

3. Галкин В. И. Промышленная электроника. – М.: Высш. шк., 1989.

4. Гольденберг Л. М. и др. Цифровые устройства на интегральных схемах в технике связи. – М.: Связь, 1979.

5. Пухальский Г. И., Новосельцева Т. Я. Проектирование дискретных устройств на интегральных микросхемах: Справочник. – М.: Радио и связь, 1990.

6. Применение интегральных микросхем в электронной вычислительной технике: Справочник / Под ред. Б. Н. Файзулаева. – М.: Радио и связь, 1986.

7. Шило В. Л. Популярные цифровые микросхемы: Справочник. – М.: Радио и связь, 1989.

8. Янсен Й. Курс цифровой электроники: В 4-х томах/Пер. с голландского. – М.: Мир, 1987.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.