При высоком напряжении на входе схемы эмиттерный переход транзистора VT1.1 закрыт, и ток через резистор R1 поступает на базу транзистора VT2, который отпирается и соответственно открываются VT3 и VT7. Транзисторы VT4 и VT6 закрыты, и на выходе устанавливается напряжение низкого уровня.

С помощью использования сложного выходного каскада на транзисторах VT4, VT6 и VT7 и диодах VD2.1 и VD2.2 в ЛЭ достигается увеличение быстродействия из - за быстрого заряда емкостей на входе схемы. Сложный входной каскад обеспечивает малые времена фронта выходного сигнала. Транзисторы VT2 и VT3 увеличивают порог переключения схемы и повышают её помехоустойчивость. Повышению помехоустойчивости способствует и корректирующая цепочка, выполненная на транзисторе VT5 и резисторах R5, R6.

Все транзисторы схемы, кроме VT1.1, VT1.2 и VT6, являются транзисторами Шотки. Транзистор VT6 не работает в режиме насыщения, поэтому использовать в место него транзистор Шотки не имеет смысла. Применение диодов и транзисторов Шотки позволяет значительно уменьшить либо полностью исключить рассасывание избыточного заряда в транзисторах схемы и повысить её быстродействие.

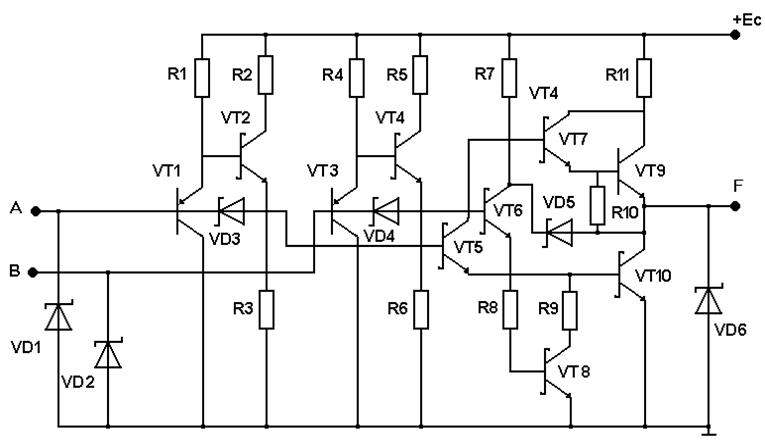

Логический элемент И-ИЛИ-НЕ реализуется схемой представленной на рис. 3.

Рис. 3 Принципиальная схема ЛЭ И-ИЛИ-НЕ серии К555.

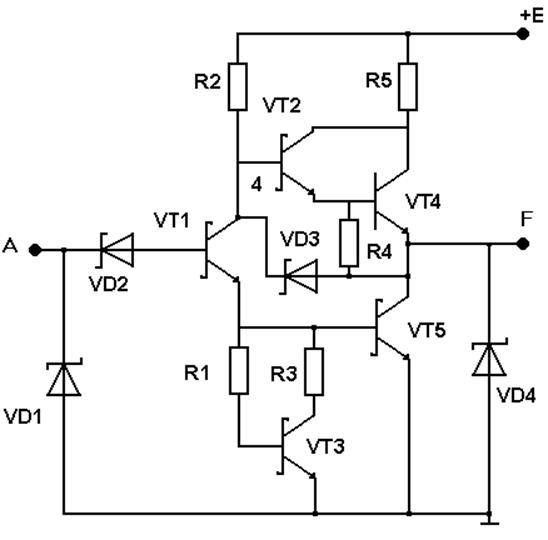

Инвертор получается из базового ЛЭ И-НЕ путём исключения диодов VD1.2, VD2.1, VD2.2, транзисторов VT1.1, VT1.2, VT2 и резисторов R1, R2, R3, рис. 4.

Рис. 4 Принципиальная схема инвертора серии К1533.

В микросхемах средней, большой и сверхбольшой интеграции электрические схемы, реализующие различные логические функции изменяются в зависимости от их назначения: буферные элементы, входные трансляторы, элементы внутренней структуры, выходные трансляторы и др.

При проектировании счётчика будут использоваться ЛЭ И-НЕ, И-ИЛИ-НЕ, НЕ.

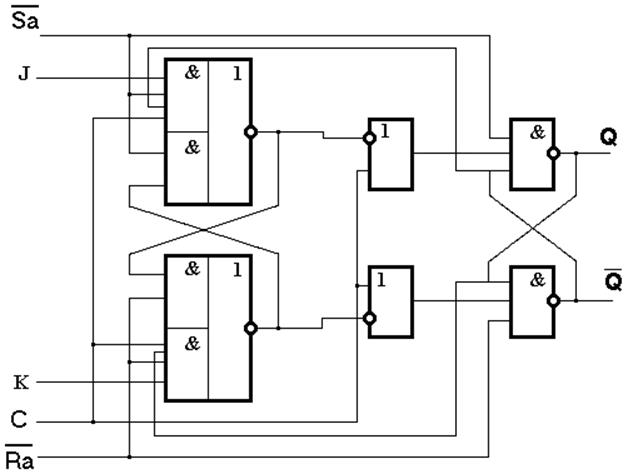

Данный триггер построен по MS-схеме, в котором ведущий триггер, синхронизируемый уровнем С=1, построен на элементах И-ИЛИ-НЕ, а ведомый, синхронизируемый уровнем С=0, - на элементах импликации и И-НЕ.

5.Синтез структурной схемы.

Структурное проектирование выполним с помощью словарного метода.

Запишем таблицу состояний счётчика (таблица 5).

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

D |

Ñ |

Ñ |

|

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

D |

|

2 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

D |

Ñ |

|

3 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

D |

|

4 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

D |

Ñ |

Ñ |

Ñ |

|

5 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

D |

|

6 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

D |

Ñ |

|

7 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

D |

|

8 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

D |

Ñ |

Ñ |

|

9 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

Ñ |

Ñ |

D |

D |

Для реализации счётчика требуется 4 триггера, причём 6 состояний счётчика будут избыточными. Используя таблицу 5, составим карты функций переходов (таблица 6).

![]()

![]()

![]()

![]()

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.