4. Синтез логических и переключательных комбинационных схем

В процессоре комбинационные схемы используются для следующих целей:

- формирование признаков X0, X1, X3, X4, X5;

- двухканальный одноразрядный мультиплексор;

- управляемый делитель частоты;

- формирователи укороченных управляющих импульсов;

- формирователи управляющих импульсов с задержкой одного из фронтов;

X0 – признак, указывающий, содержит ли счетчик значение 255 (все единицы), реализуется на схеме 8И-НЕ.

X1 – признак, указывающий, содержит ли счетчик значение 0 (все нули), реализуется на схеме 8ИЛИ. Так как такая ИМС отсутствует в серии, признак реализован на схемах 3ИЛИ-НЕ, 2ИЛИ-НЕ, которые затем собраны на элементе 4И-НЕ.

X3 – признак, указывающий, содержит ли счетчик значение 0 (все нули), реализуется на схеме 8ИЛИ. Так как такая ИМС отсутствует в серии, признак реализован на схемах 2ИЛИ-НЕ, которые затем собраны на элементе 4И-НЕ.

X4 – признак нарушения нормализации мантиссы влево. Равен нулю, если два старших бита мантиссы одинаковы, а остальная ее часть не равна нулю. Сравнение старших разрядов реализовано на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ, признак равенства нулю остальной части мантиссы – на элементе 22ИЛИ, который реализован на элементах 3ИЛИ-НЕ, НЕ, 8И-НЕ. Оба признака собираются вместе на элементе 2И-НЕ.

X5 – признак нарушения нормализации мантиссы вправо. Равен единице, если число единичных бит на входе нечетно. На его входы поданы значения: знаки мантисс исходных операндов, знак мантиссы результата, выходной перенос после сложения. Схема контроля четности реализована на трех элементах ИСКЛЮЧАЮЩЕЕ ИЛИ, включенных каскадно.

Формирователи укороченных управляющих импульсов основаны на логической сборке соответствующих признаков разрешения выдачи импульса с импульсами от тактового генератора. В связи с их простотой их подробное рассмотрение нецелесообразно.

Формирователи управляющих импульсов с задержкой одного из фронтов основаны на том, что для формирования единичного уровня на выходе элемента 2И-НЕ достаточно иметь на любом из входов 0, а для нулевого уровня на выходе – 1 на обоих входах. Если на один из входов подать сигнал, задержанный относительно другого, то на выходе 1 будет формироваться сразу, а 0 – с задержкой. Для формирования задержки сигнала использована цепочка из двух инверторов.

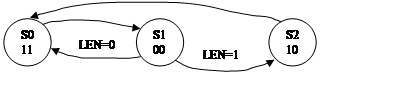

Управляемый делитель частоты представляет собой синхронный автомат, собранный на JK-триггерах.

|

LEN |

Q1(t) |

Q0(t) |

Q1(t+1) |

Q0(t+1) |

J1 |

K1 |

J0 |

K0 |

||

|

0 |

0 |

0 |

1 |

1 |

1 |

* |

1 |

* |

||

|

0 |

0 |

1 |

* |

* |

* |

* |

* |

* |

||

|

0 |

1 |

0 |

1 |

1 |

* |

0 |

1 |

* |

||

|

0 |

1 |

1 |

0 |

0 |

* |

1 |

* |

1 |

||

|

1 |

0 |

0 |

1 |

0 |

1 |

* |

0 |

* |

||

|

1 |

0 |

1 |

* |

* |

* |

* |

* |

* |

||

|

1 |

1 |

0 |

1 |

1 |

* |

0 |

1 |

* |

||

|

1 |

1 |

1 |

0 |

0 |

* |

1 |

* |

1 |

В результате оптимизации получим:

J1= /Q0

/K1 = /Q0

/K0 = /Q0

J0= /LEN + Q1 = /(LEN * /Q1)

LEN – вход управления коэффициентом деления, если LEN=0 коэффициент равен 2, если LEN=1 коэффициент равен 3.

5. Разработка и описание работы принципиальной электрической схемы

При включении питания процессора происходит его сброс следующим образом:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.