IEEE и VAX форматы вещественных чисел одинарной и двойной точности

-конвейерное (7 ступеней) целочисленное устройство

-устройство управления памятью

-страничная память

-48-входовый полностью ассоциативный буфер трансляции инструкций

-64-входовый полностью ассоциативный буфер трансляции данных

-каждый вход буфера трансляции способен отображать 1,8,64 или 512

8К-байтных страниц

-8 Кб с прямым отображением кеш данных первого уровня с прямой записью

-8 Кб с прямым отображением кеш инструкций первого уровня

-96 Кб 3-входовый наборно-ассоциативный кеш второго уровня на чипе для команд и данных

-буфер записи на чипе с 6-ю полностью ассоциативными 32-разрядными входами

-высокопроизводительный интерфейс

-128-битная шина процессор-память

-контроль по четности или код с коррекцией ошибок (ECC) по выбору

-40-битная адресация

-программируемая временная диаграмма интерфейса

-контроллер для внешнего Кеша третьего уровня

-поддержка синхронного и асинхронного ОЗУ

-программируемый размер блока в Кеше

-программируемые счетчики производительности для определения скорости процессора и системы

-последовательный интерфейс с ПЗУ-загрузка Кеша инструкций после сброса

-тестирование на уровне кристалла и модуля, поддержка JTAG(IEEE 1149.1)

-корпус с матричным расположением выводов IPGA

-поддержка архитектуры привилегированных инструкций (PALcode)

-оптимизация для разных ОС

-гибкое управление памятью

-выполнение неразрывных последовательностей инструкций

-потребляемая мощность на частоте 366 МГц: 28 Вт (+5 Вт на каждые 66 МГц)

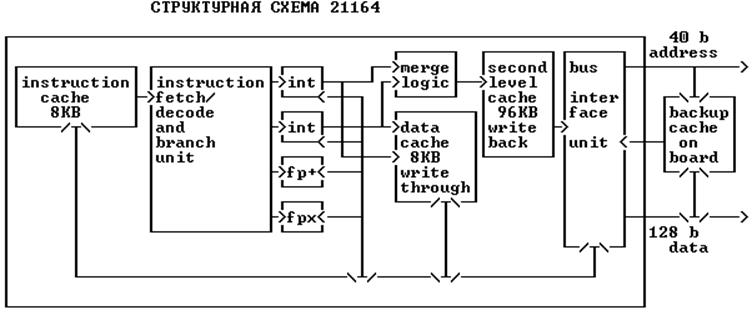

21164 состоит из пяти независимых функциональных частей:

-устройство выборки инструкций ,декодирования и переходов

-выбирает ,декодирует и посылает инструкции в целочисленное устройство, устройство с плавающей точкой и устройство управления памятью

-управляет конвейерами, программным счетчиком, кешем инструкций, предвыборкой и потоком инструкций

-декодирует до 4-х инструкций параллельно и проверяет на доступность требуемые ресурсы

-целочисленное исполнительное устройство

-содержит два 64-битных целочисленных конвейера

-результаты большинства целочисленных операций доступны для последующих инструкций

-частично исполняет все инструкции ,относящиеся к памяти, вычисляя эффективные адреса

-устройство управления памятью

-обрабатывает все инструкции загрузки и записи

-две инструкции загрузки могут выполняться параллельно (двух портовый кеш данных)

-до 21 инструкции могут выполняться параллельно

-управление Кешем данных и логикой, которая реализует и объединяет инструкции загрузки, для которых нет данных в кеше данных

-устройство интерфейса с шиной и управления кешем L3

-обрабатывает все операции доступа к памяти, которые инициирует устройство управления памятью и все внешние функции, относящиеся к памяти

-следит за когерентностью Кеша

-управляет Кешем L2 и L3

-устройство с плавающей точкой

-содержит конвейер сложения и конвейер умножения вещественных чисел (операция деления связана с конвейером сложения, но не конвейеризуется сама по себе)

виртуальное адресное пространство виртуальный адрес 64-битное без знаковое целое число, которое определяет положение байта в пространстве виртуальных адресов; микропроцессор использует 43-битное подмножество виртуальных адресов и поддерживает 40-битное физическое адресное пространство 1 Гб

МИКРОПРОЦЕССОР ALPHA 21264

-суперскалярная архитектура (4 входа для команд)

-динамическое планирование, переименование регистров и спекулятивное выполнение инструкций

-порядок выполнения инструкций может отличаться от записанного в программе для повышения производительности

-4 целочисленных исполнительных устройства 2 из них могут выполнять

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.