ARM режим микропроцессора ARM7TDMI

Введение

ARM7TDMI - член RISC (ARM) семейства универсальных 32-разрядных микропроцессоров, которые предлагают высокую эффективность при очень низкой потребляемой мощности и цене.

Архитектура ARM основана на Reduced Instruction Set Computer (RISC) принципе. Система команд и декодирующий механизм, намного более просты чем микропроцессоры с расширенной системой команд. Эта простота приводит к высокой производительности выполнения команд и минимальному времени ответа прерывания в реальном масштабе времени.

Конвейерная обработка используется так, чтобы все части обработки и систем памяти могли работать непрерывно. Как правило, в то время как одна команда выполняется, ее преемник декодируется, и третья команда выбирается от памяти.

Архитектура ARM7TDMI

ARM7TDMI - конвейерный, 32-разрядный процессор RISC с 3 уровнями конвейера. Архитектура процессора - Фон Neumann, которая характеризуется единственной шиной данных и адреса для команд и данных. Центральный процессор имеет две системы команд: ARM и THUMB. Система команд ARM имеет 32-разрядные команды и обеспечивает максимальную производительность. Команды оперируют с 8-, 16-, и 32-разрядными типами данных.

Центральный процессор имеет семь операционных режимов. Каждый операционный режим имеет свои banked регистры для быстрой обработки особых ситуаций. Процессор имеет 37 32-разрядных регистров, включая 6 регистраторов состояния.

Режимы процессора

С точки зрения программиста, ARM7TDMI может быть в одном из двух состояний:

· Состояние ARM, в котором выполняются 32-разрядные команды.

· Состояние THUMB, который работает с 16-разрядными командами. В этом состоянии, PC использует 1-ый бит, чтобы выбрать между состояниями.

Обратите внимание: Переход между этими двумя состояниями не затрагивает режим процессора или содержание регистров.

Переключение Состояний

Переключение в состояние THUMB

Вход в состояние THUMB может быть выполнено, при помощи команды BX с битом состояния (бит 0) в регистре операнда.

Переход в состояние THUMB также произойдет автоматически по возвращению из исключений (IRQ, FIQ, UNDEF, ABORT, SWI и т.д.), если исключение произошло с процессором в состоянии THUMB.

Переключение в состояние ARM

Вход в состояние ARM происходит:

1. При выполнении команды BX со сброшенным битом состояния, в регистре операнда.

2. Когда процессор выполняет исключения (IRQ, FIQ, UNDEF, ABORT, SWI и т.д.).

В этом случае, в регистре PC помещается значение регистра ссылки режима исключения, и выполнение начинается с векторного адреса исключения.

Режимы процессора.

ARM7TDMI поддерживает семь режимов работы:

User (usr): Нормальное состояние выполнения программы ARM

FIQ (fiq): Предназначенны, чтобы поддержать передачу данных

IRQ (irq): Используемый для универсальной обработки прерывания

Supervisor (svc): Защищенный режим для операционной системы

Abort mode (abt): Аварийное завершение работы

System (sys): Привилегированный режим для операционной системы

Undefined (und): Происходит когда пытается выполниться неопределенная команда.

Изменения режима могут быть сделаны программно, или могут быть вызваны внешними прерываниями или обработкой исключения. Большинство прикладных программ выполнится в Непривилегированном режиме. Не пользовательские режимы - известный как привилегированные режимы - используется, чтобы обслужить прерывания или исключения, или обращаться к защищенным ресурсам.

Регистры

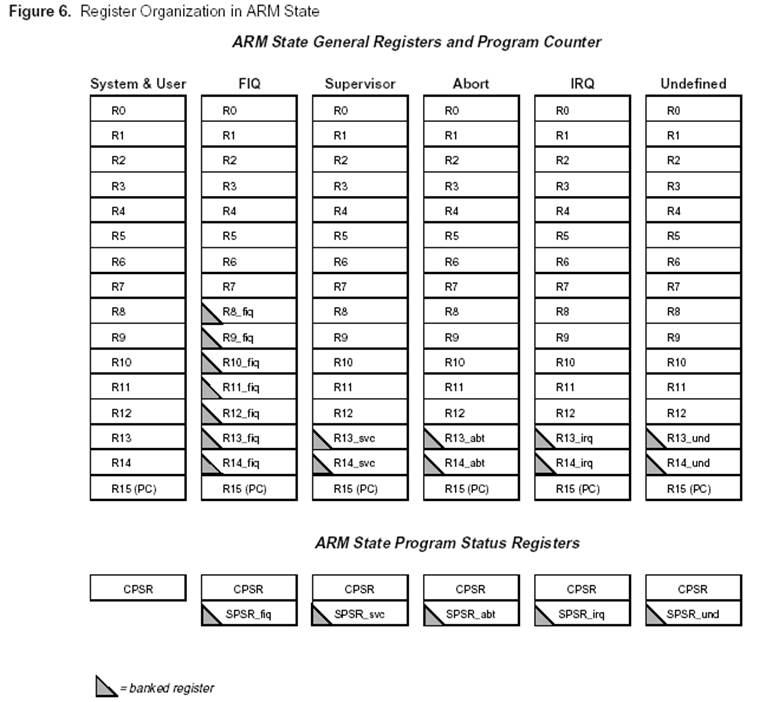

ARM7TDMI имеет общее количество 37 регистров - 31 универсального 32-разрядных регистров и шести регистров состояния - но они не могут все быть видимы сразу. Состояние процессора и операционный режим диктуют, какие регистры являются доступными программисту.

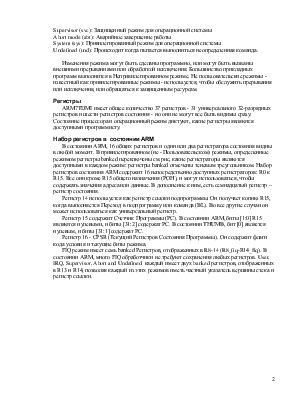

Набор регистров в состоянии ARM

В состоянии ARM, 16 общих регистров и один или два регистратора состояния видны в любой момент. В привилегированном (не - Пользовательском) режимы, определенные режимом регистры banked переключены см.рис, какие регистраторы являются доступными в каждом режим: регистры banked отмечены теневым треугольником. Набор регистров состояния ARM содержит 16 непосредственно доступных регистраторов: R0 к R15. Все они кроме R15 общего назначения (РОН), и могут использоваться, чтобы содержать значения адреса или данные. В дополнение к ним, есть семнадцатый регистр – регистр состояния.

Регистр 14 используется как регистр ссылки подпрограммы. Он получает копию R15, когда выполняется Переход в подпрограмму или команда (BL). Во все другие случаи он может использоваться как универсальный регистр.

Регистр 15 содержит Счетчик Программы (PC). В состоянии ARM, биты [1:0] R15 являются нулевыми, и биты [31:2] содержат PC. В состоянии THUMB, бит [0] является нулевым, и биты [31:1] содержат PC.

Регистр 16 - CPSR (Текущий Регистров Состояния Программы). Он содержит флаги кода условия и текущие биты режима.

FIQ режим имеет семь banked Регистров, отображенных в R8-14 (R8_fiq-R14_fiq). В состоянии ARM, много FIQ обработчики не требуют сохранения любых регистров. User, IRQ, Supervisor, Abort and Undefined каждый имеет двух banked регистров, отображенных в R13 и R14, позволяя каждый из этих режимов иметь частный указатель вершины стека и регистр ссылки.

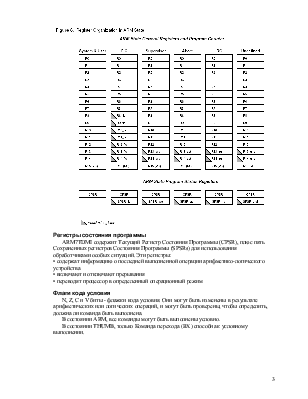

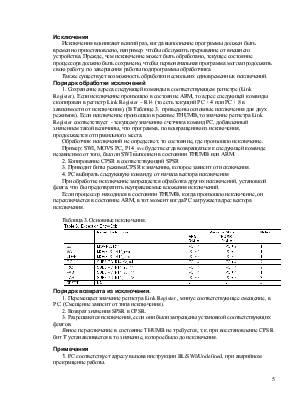

Регистры состояния программы

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.