ARM7TDMI содержит Текущий Регистр Состояния Программы (CPSR), плюс пять Сохраненных регистров Состояния Программы (SPSRs) для использования обработчиками особых ситуаций. Эти регистры:

• содержат информацию о последней выполненной операции арифметико-логического устройства

• включают и отключают прерывания

• переводят процессор в определенный операционный режим

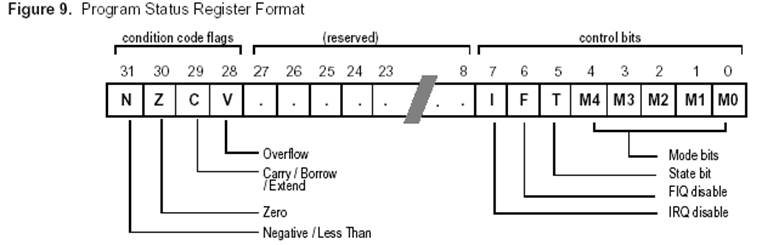

Флаги кода условия

N, Z, C и V биты - флажки кода условия. Они могут быть изменены в результате арифметических или логических операций, и могут быть проверены, чтобы определить, должна ли команда быть выполнена.

В состоянии ARM, все команды могут быть выполнены условно.

В состоянии THUMB, только Команда перехода (BX) способна к условному выполнении.

Служебные биты

Последние 8 бит PSR (I, F, T и М. [4:0]) известны вместе как служебные биты. Они будут, изменятся, когда возникает исключение. Если процессор работает в привилегированном режиме, они могут также меняться при помощи программного обеспечения.

Бит T - отражает операционное состояние. Когда этот бит, установлен, процессор работает в состоянии THUMB, иначе это состояние ARM. Это также отражается на внешнем сигнале TBIT. Обратите внимание, что программное обеспечение никогда не должно изменять состояние TBIT в CPSR. Если это произойдет, то процессор поведет себя не предсказуемым образом.

Прерывание отключает биты, I и F. Когда эти биты установлены, они отключают запрос на прерывание и прерывание FIQ соответственно.

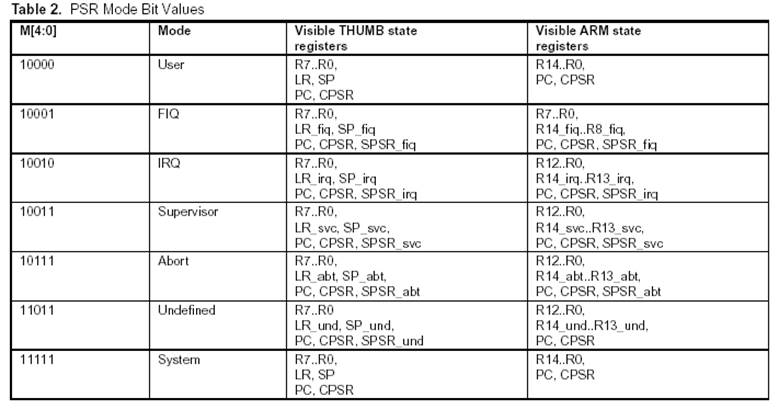

Биты режима M4,

M3, M2, M1 и M0 биты (М. [4:0]) являются битами режима. Они определяют

операционный режим процессора, как показано в Таблице.  Не все комбинации битов

режима определяют допустимый режим процессора. Только явно описанные здесь режимы

могут быть использованы.

Не все комбинации битов

режима определяют допустимый режим процессора. Только явно описанные здесь режимы

могут быть использованы.

Зарезервированные биты остающиеся биты в PSRs зарезервированы. При изменении флагов PSR или служебных битов, Вы должны быть уверены, что эти неиспользованные биты, будут неизменны.

Исключения

Исключения возникают всякий раз, когда выполнение программы должен быть временно приостановлено, например чтобы обслужить прерывание от внешнего устройства. Прежде, чем исключение может быть обработано, текущее состояние процессора должно быть сохранено, чтобы первоначальная программа могла продолжить свою работу, по завершения работы подпрограммы обработчика.

Также существует возможность обработки нескольких одновременных исключений. Порядок обработки исключений

1. Сохранение адреса следующей команды в соответствующем регистре (Link Register). Если исключение произошло в состояние ARM, то адрес следующей команды скопирован в регистр Link Register – R14 (то есть текущий PC + 4 или PC + 8 в зависимости от исключения). (В Таблице 3. приведены основные исключения для двух режимов). Если исключение произошло в режиме THUMB, то значение регистра Link Register соответствует - текущему значению счетчика команд PC, добавленный значением такой величины, что программа, по возвращению из исключения, продолжается от правильного места.

Обработчик исключений не определяет, то состояние, где произошло исключение.

Пример: SWI, MOVS PC, Р14_svc будет всегда возвращаться к следующей команде независимо от того, был ли SWI выполнен в состоянии THUMB или ARM.

2. Копирование CPSR в соответствующий SPSR

3. Приводит биты режима CPSR к значению, которое зависит от исключения.

4. PC выбирать следующую команду, от начала вектора исключения

При обработке исключение запрещается обработка других исключений, установкой флага, что бы предотвратить неуправляемые вложения исключений.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.