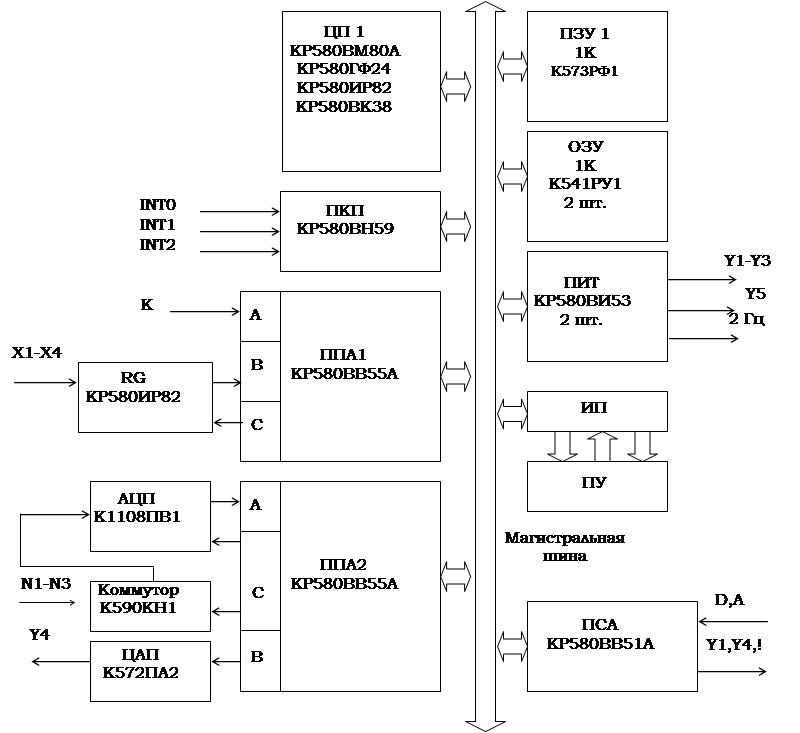

На рис. 4 использованы следующие обозначения:

V1, V2, V3 — аналоговые сигналы, поступающие через аналоговый мультиплексор МПР на вход АЦП;

X1, X2, X3, X4, Х5—цифровые двоичные сигналы, формируемые соответственно датчиками Д1, Д2, Д3, Д4;

Y1, Y2, Y3 — одноразрядные управляющие сигналы, вырабатываемые МК и поступающие на исполнительные механизмы;

Y4 — 8-разрядный код, преобразуемый в аналоговый сигнал ЦАП;

INT0 – INT2 - запросы на прерывание;

ИП - интерфейс пользователя для подключения к МПС пульта управления ПУ.

Подключение необходимого аналогового сигнала производится с помощью коммутатора К590КН6.

В программах МПС обращение к регистрам периферийных БИС производится по командам чтения/записи порта(IN/OUT).

|

Микропроцессор - это функционально законченное программно управляемое устройство для обработки цифровой информации и управляющее процессом обработки, реализованное на одной или нескольких больших интегральных схемах (БИС). Номенклатура БИС, предназначенная для работы с данным микропроцессором, называется микропроцессорным комплектом. Электрические характеристики комплекта и его функциональные возможности в первую очередь зависят от БИС центрального процессора (ЦП). В основе применяемого в данной МПС микропроцессорного комплекта лежит микропроцессор I8080 фирмы Intel, отечественным аналогом которого является МП КР580.

Микропроцессор КР580ВМ80 обладает 8 битной шиной данных, и 16-ти разрядной шиной данных, что позволяет адресовать на прямую до 64К памяти ОЗУ или ПЗУ. Наличие входа INT позволяет применять контроллер прерываний.

Стандартная схема подключения процессора содержит два шинных формирователя на базе регистров КР580ИР82. Системный контроллер для чтения выдачи информации на шину данных. Нагрузочная способность выводов этих элементов составляет 10 ТТЛ входов. Для синхронизации работы процессора с памятью и другими внешними устройствами применяется генератор тактовых импульсов КР580ГФ24. Частота следования синхроимпульсов F1 и F2 в девять раз меньше частоты кварцевого резонатора. Для получения оптимальной для микропроцессора тактовой частоты 2 МГц используется кварцевый резонатор частотой 18 МГц. Сопротивление кварцевого резонатора носит ёмкостной характер. Это приводит к нестабильной работе генератора. Для компенсации ёмкостной составляющей резонатора последовательно с ним включается конденсатор емкостью 20 пФ.

Сигналы HOLD, HLDA и BUSEN реализуют режим прямого доступа к магистрали со стороны других активных модулей системы. Так как такой режим не предусмотрен, сигналы HOLD и BUSEN заземляются.

Питание БИС микропроцессорного комплекта осуществляется от внешнего источника питания напряжением 5В.

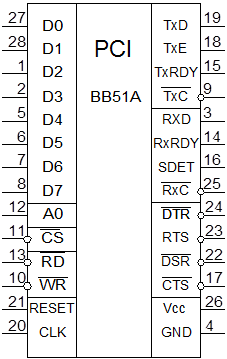

Реализация асинхронного канала связи МПС с удаленным терминалом осуществлена на основе БИС универсального синхронно-асинхронного приемопередатчика КР580ВВ51А.

Программно осуществляется обмен информацией между МПС и ЭВМ. В зависимости от запроса терминала (символы “D” или “A)”, полученного по обратному каналу данных - от терминала к МПС, система выдает соответственно либо результат обработки цифровых датчиков Y1, либо результат обработки аналоговой информации Y4.

Синхронизация работы БИС осуществляется от первого канала программируемого интервального таймера.

Микросхема КР580ВВ51А, представленная на рисунке 3, применяется для организации двунаправленного обмена данными в последовательном формате между микропроцессором и внешним устройством. Обмен информацией с микроЭВМ осуществляется по 8-разрядной двунаправленной шине данных.

Схема программно может быть установлена в один из

пяти режимов работы: асинхронная передача, асинхронный прием, синхронная

передача, синхронный прием данных с внутренней синхронизацией, синхронный прием

с внешней синхронизацией. При программно-управляемой передаче используется

слово состояния ПСА SW.

Схема программно может быть установлена в один из

пяти режимов работы: асинхронная передача, асинхронный прием, синхронная

передача, синхронный прием данных с внутренней синхронизацией, синхронный прием

с внешней синхронизацией. При программно-управляемой передаче используется

слово состояния ПСА SW.

Максимальная скорость обмена информацией осуществляется в синхронном (56000Бит/с) или в асинхронном (9600Бит/с) режимах. Длина передаваемых символов 5-8 разрядов. При передаче схема преобразует данные в параллельном коде в последовательность символов со служебной информацией и выдает ее в канал с различной скоростью.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.