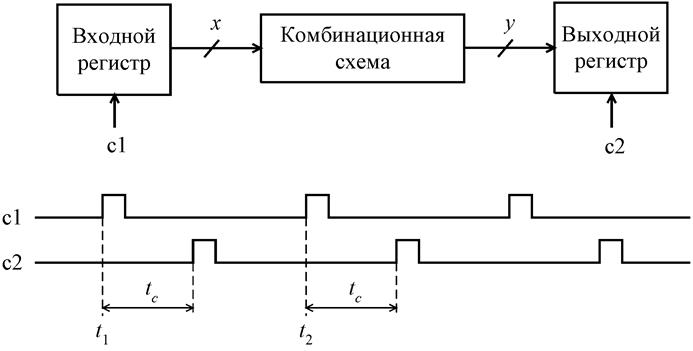

Временная задержка (delay fault) есть модель повреждений, которые вызывают неправильную работу логических схем относительно тактовой частоты. Это можно пояснить схемой на рис. 4.50.

Рис.4.50.

По сигналу С1 переменные х из входного регистра подаются на вход схемы. По

сигналу С2 выходные сигналы y

записываются в выходной регистр. Пусть ![]() есть

время от момента изменения входных сигналов х до момента изменения всех выходных сигналов y . Оно равно времени прохождения сигнала по самому

длинному пути в схеме.

есть

время от момента изменения входных сигналов х до момента изменения всех выходных сигналов y . Оно равно времени прохождения сигнала по самому

длинному пути в схеме.

Если окажется, что ![]() , то в выходном регистре будут записаны

неправильные значения сигналов y. Цель тестирования задержек удостовериться, что каждый путь в схеме

имеет время прохождения сигнала меньше чем

, то в выходном регистре будут записаны

неправильные значения сигналов y. Цель тестирования задержек удостовериться, что каждый путь в схеме

имеет время прохождения сигнала меньше чем ![]() .

.

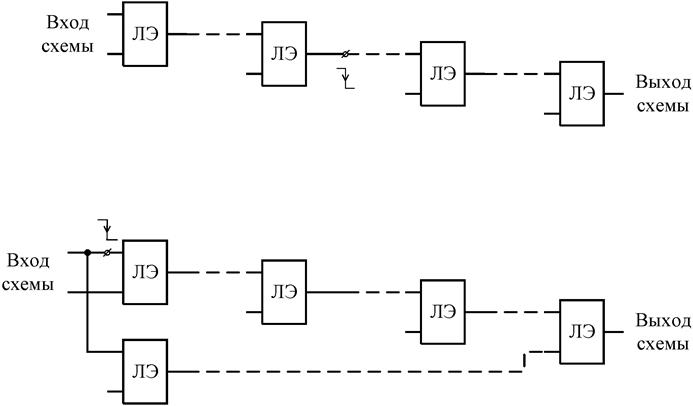

Рассматриваются две модели временных неисправностей:

задержка элемента (gate delay fault) – моделирует дефекты, которые вызывают реальную задержку распространения сигнала через отдельный элемент, превышающую их спецификацию;

задержка пути (path delay fault) – моделирует задержку сигнала, возникающую в результате суммирования распределенных задержек всех элементов пути.

При этом различают два вида

задержек – ВЗ возрастающего перехода сигнала 0 ![]() 1 (рис.

4.51,а) и ВЗ убывающего перехода сигнала 1

1 (рис.

4.51,а) и ВЗ убывающего перехода сигнала 1 ![]() 0 (рис.

4.51,б).

0 (рис.

4.51,б).

Рис.4.51.

Для обнаружения ВЗ на вход схемы надо

последовательно подать два набора ![]() и

и ![]() . Набор

. Набор ![]() ,

«устанавливающий», должен установить сигнал 1 (для задержки 1

,

«устанавливающий», должен установить сигнал 1 (для задержки 1 ![]() 0) или сигнал 0 (для задержки 0

0) или сигнал 0 (для задержки 0 ![]() 1) на той линии схемы, откуда начинается

изменение (перепад) логического сигнала. Для ВЗ элемента такой линией является

выходная линия элемента (рис. 4.52,а), для ВЗ пути – вход элемента, с которого

начинается данный путь (рис. 4.52,б).

1) на той линии схемы, откуда начинается

изменение (перепад) логического сигнала. Для ВЗ элемента такой линией является

выходная линия элемента (рис. 4.52,а), для ВЗ пути – вход элемента, с которого

начинается данный путь (рис. 4.52,б).

Рис.4.52.

При тестировании набор ![]() подается в момент времени

подается в момент времени ![]() (см. рис. 4.50) по сигналу С1. После того,

как все сигналы y устанавливаются,

в момент времени

(см. рис. 4.50) по сигналу С1. После того,

как все сигналы y устанавливаются,

в момент времени ![]() по сигналу С1 подается набор

по сигналу С1 подается набор ![]() . Набор

. Набор ![]() ,

«продвигающий», должен выполнить две задачи: 1) установить на линии схемы, с

которой начинается изменение логического сигнала, сигнал 0 (для перепада 1

,

«продвигающий», должен выполнить две задачи: 1) установить на линии схемы, с

которой начинается изменение логического сигнала, сигнал 0 (для перепада 1 ![]() 0) или сигнал 1 (для перепада 0

0) или сигнал 1 (для перепада 0 ![]() 1); 2) обеспечить наличие хотя бы одного

чувствительного пути от этой линии до выхода схемы. В момент времени

1); 2) обеспечить наличие хотя бы одного

чувствительного пути от этой линии до выхода схемы. В момент времени ![]() (см. рис. 4.50) производится измерение

выходных сигналов и сравнение их с эталонными сигналами, которые должны быть у

исправной схемы.

(см. рис. 4.50) производится измерение

выходных сигналов и сравнение их с эталонными сигналами, которые должны быть у

исправной схемы.

Рассмотрим схему на рис. 4.53.

Рис.4.53.

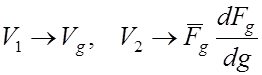

Пусть надо найти тест ![]() для ВЗ элемента 2 типа 1

для ВЗ элемента 2 типа 1 ![]() 0. Обозначим выход элемента 2 через g и задержку 1

0. Обозначим выход элемента 2 через g и задержку 1 ![]() 0

на линии g как

0

на линии g как ![]() . Пусть

. Пусть ![]() – функция, реализуемая на линии g. Тогда

– функция, реализуемая на линии g. Тогда

.

(4.41)

.

(4.41)

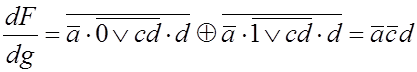

Найдем

.

.

Имеем ![]() ,

, ![]() и тест

и тест ![]() . На

рис. 4.53 показаны изменения сигналов на линиях схемы при поступлении на ее

входы данного теста. Набор

. На

рис. 4.53 показаны изменения сигналов на линиях схемы при поступлении на ее

входы данного теста. Набор ![]() = 0101 обеспечивает на

линии g сигнал 1. Набор

= 0101 обеспечивает на

линии g сигнал 1. Набор ![]() = 0001 устанавливает на линии g сигнал 0 и создает чувствительный

путь b–2–4–5–6–F. Задержка изменения сигнала 1

= 0001 устанавливает на линии g сигнал 0 и создает чувствительный

путь b–2–4–5–6–F. Задержка изменения сигнала 1 ![]() 0

на выходе элемента 2 вызовет соответствующую задержку сигнала на выходе схемы.

0

на выходе элемента 2 вызовет соответствующую задержку сигнала на выходе схемы.

Рассмотрим теперь пример

неисправности типа ВЗ пути. Обозначим пути схемы на рис. 4.53 следующим

образом: ![]() ;

; ![]() ;

; ![]() ;

; ![]() ;

; ![]() ;

; ![]() .

.

Рассмотрим неисправность ![]() . Найдем производную

. Найдем производную

![]() .

.

Согласно (4.41) имеем

![]()

![]() .

.

Получаем тест ![]() тот

же, что и тест для неисправности

тот

же, что и тест для неисправности ![]() .

.

Из сравнения данных двух неисправностей видно, что модель «задержка пути» является более общей чем модель «задержка элемента», поскольку выходная линия элемента всегда входит хотя бы в один путь. Поэтому в дальнейшем будем говорить о ВЗ путей.

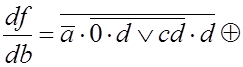

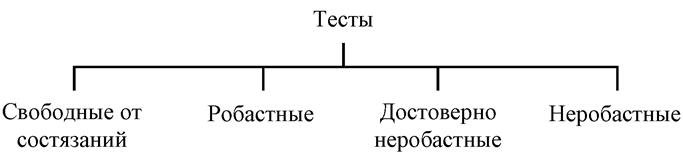

На рис. 4.54 и 4.55

показаны классификация тестов ![]() и классификация

неисправностей.

и классификация

неисправностей.

Рис.4.54.

Рис.4.55.

Тест называется свободным от состязаний, если для всех элементов, входящих в чувствительный путь, выполняется условие: логический сигнал изменяется только на одном входе.

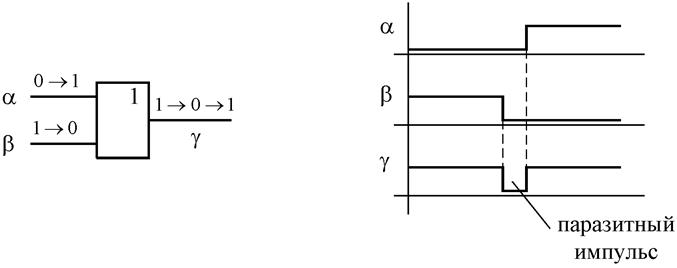

Состязания на входах элемента возникают при одновременном изменении сигналов на двух или более входах. В этом случае на выходе элемента может появиться паразитный импульс (рис. 4.56).

Рис.4.56.

Из рис. 4.53 следует, что тест (0101, 0001) является свободным от состязаний.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.