Второе допущение также очень важно для константных неисправностей. Для нашего примера (рис. 4.3) оно говорит о том, что неисправный элемент продолжает работать как элемент ИЛИ-НЕ, а не превращается, например, в схему «Сложение по модулю 2» или в схему с памятью (триггер). Если же в результате повреждения логика элемента изменяется, то, как правило, не выполняется и первое допущение, а задача обнаружения неисправностей существенно усложняется. Третье допущение существенно упрощает модель, снимая трудности, которые возникают при обнаружении временных и перемежающихся отказов.

Эффективность модели определяется покрытием неисправностей. Говорят, что данная модель покрывает данную физическую неисправность, если последняя обнаруживается тестом, построенным для данной модели. Тесты для константных моделей обладают высоким покрытием неисправностей. В зависимости от технологии изготовления логических схем это покрытие составляет 80–95%. Однако в микроэлектронных схемах с высокой степенью интеграции существуют классы неисправностей, которые не описываются константными моделями. Рассмотрим наиболее распространенные такие модели.

Установлено, что вход-выходное поведение неисправных логических схем, выполненных по МОП- и КМОП-технологиям, не может быть всегда точно описано моделью константных неисправностей. В этом случае применяется модель транзистора как простого идеального переключателя (по аналогии с контактом в контактных схемах). Данная модель предполагает, что повреждения транзисторов могут быть двух видов (как у контактов): постоянное размыкание (stuck–open fault) и постоянное замыкание (stuck–short fault). В дальнейшем эти неисправности будем называть «обрыв» и «замыкание» транзистора.

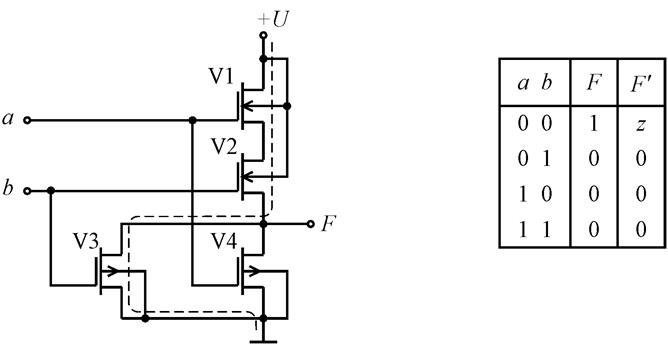

На рис. 4.4 представлен элемент ИЛИ-НЕ, выполненный по КМОП- технологии.

Рис.4.4. Элементы ИЛИ-НЕ

Он состоит из двух Р- канальных МОП- транзисторов V1 и V2, включенных последовательно, и двух n-канальных транзисторов V3 и V4, включенных параллельно. Если a= b = 0, то оба транзистора V1 и V2 открыты, а оба транзистора V3 и V4 закрыты. В результате выход элемента F изолируется от земли и соединяется с полюсом питания U. На выходе F присутствует логический сигнал 1.

Если на одном из входов a или b (или на обеих) имеется сигнал 1, то соответствующий транзистор V1 или V2 (или оба) закрывается, а один из транзисторов V3 или V4 (или оба) открывается. В результате выход F изолируется от полюса U и подключается к земле; на нем устанавливается сигнал 0.

Рассмотрим неисправность

типа «обрыв» транзистора V1. Если a =

b = 0, то транзисторы V1 и V2 открыты

в исправной схеме, но закрыты в неисправной схеме. Транзисторы V3 и V4 закрыты

в обеих схемах. Таким образом, выход F равен 1 в исправной схеме и «плавает»,

т.е. имеет неопределенное значение (не соединен ни с полюсом U, ни с землей) в

неисправной схеме. Это значение обозначается как Z. На рис. 4.4, б в столбце ![]() показано поведение неисправного элемента.

В реальных КМОП-схемах узел F будет иметь

некоторую паразитную емкость, заряд которой определяется предыдущим состоянием

элемента. Чтобы обнаружить данную неисправность надо сигнал Z заменить на

сигнал 0. При этом поведение неисправной схемы будет отличаться от поведения

исправной (в первой строке на рис. 4.4, б). Для этого перед подачей вектора AB = 00 подается вектор AB = 10, который устанавливает в

неисправной схеме на выходе F сигнал 0,

обеспечивая разряд емкости узла F на землю. Полный тест содержит два вектора 10

показано поведение неисправного элемента.

В реальных КМОП-схемах узел F будет иметь

некоторую паразитную емкость, заряд которой определяется предыдущим состоянием

элемента. Чтобы обнаружить данную неисправность надо сигнал Z заменить на

сигнал 0. При этом поведение неисправной схемы будет отличаться от поведения

исправной (в первой строке на рис. 4.4, б). Для этого перед подачей вектора AB = 00 подается вектор AB = 10, который устанавливает в

неисправной схеме на выходе F сигнал 0,

обеспечивая разряд емкости узла F на землю. Полный тест содержит два вектора 10 ![]() 00,

которые вызывают изменение сигнала на выходе 0

00,

которые вызывают изменение сигнала на выходе 0 ![]() 1 в

исправной схеме и 0

1 в

исправной схеме и 0 ![]() 0 в неисправной схеме. Алгоритмы

генерации тестов должны формировать эти пары векторов. Таким образом, в этом

случае неисправная схема обладает некоторой памятью, то есть нарушается второе

допущение для константных неисправностей.

0 в неисправной схеме. Алгоритмы

генерации тестов должны формировать эти пары векторов. Таким образом, в этом

случае неисправная схема обладает некоторой памятью, то есть нарушается второе

допущение для константных неисправностей.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.