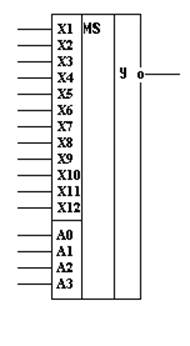

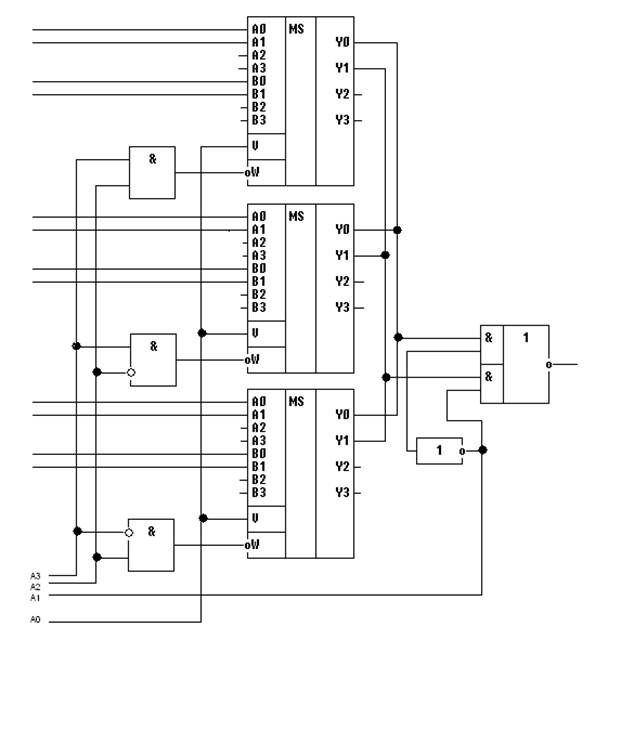

Условное графическое изображение полученного мультиплексора(рис.3).

Рис.3

Описание работы:

При подаче на адресные входы код требуемого входа, происходит переключение:

Если А3 – «1», происходит переключение на нижний вход от выхода У3 предыдущей микросхемы, но только в том случае если А2 =0, если – «0», на входе информация от У1 или У2 той же микросхемы, в зависимости от А2.

В зависимости от А1 выбирается, какой канал из 2х будет рабочим, а от А0 зависит, какой вход будет принимать информацию.

Задача № 4

1. Разработать схему счётчика, выполненного на счётчиках меньшей разрядности и триггерах D и JK, считающую по модулю 63. Применяемые счётчики – ИЕ5.

2. Построить временную диаграмму.

3. Определить требуемое число корпусов и быстродействие.

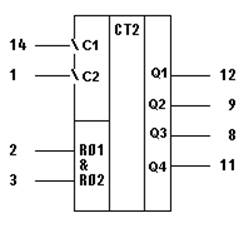

1. УГО используемых счётчиков 555ИЕ5 (рис.1):

Рис.1

Используемый логический элемент : 7И, который можно построить на основе элемента 8И-НЕ микросхемы К155ЛА2, заземлив через инвертор лишний вход и поставив на выходе инвертор.

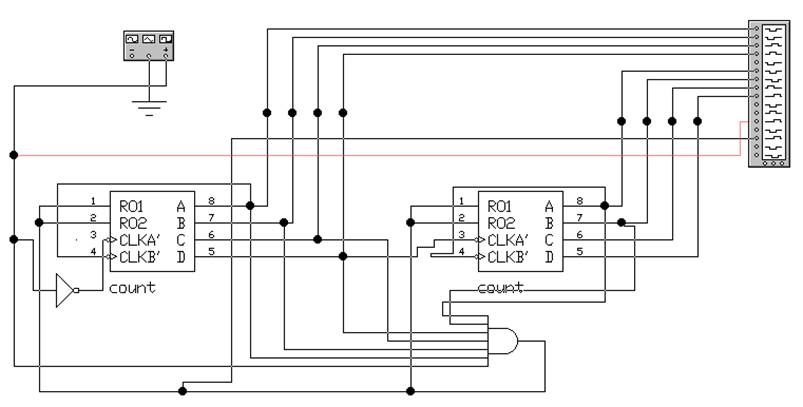

Для построения схемы воспользуемся пакетом EWB в котором вместо заданного используем стандартный 4-х разрядный счётчик, отличающийся от заданного только типом синхронизации. Функциональная схема приведена на рис. 2.

Рис.2

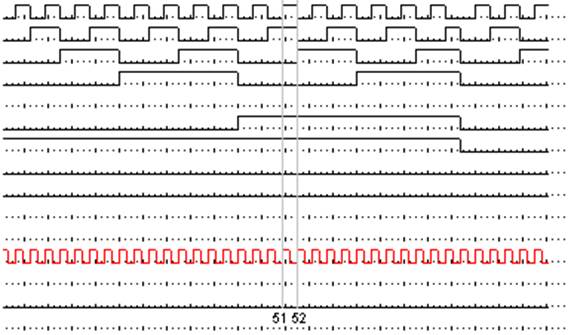

2. Получим с помощью логического анализатора временную диаграмму (рис. 3).

Рис. 3

3. Для построения схемы необходимо 4 микросхемы: 2 – 555ИЕ5, 1 – 555ЛА2, 1 – 555ЛН1

tз=tз инв+tз сч

Задача № 6

Предложите нестробируемый мультиплексор размерностью Nз->1 на базе стробированых MUX размерностью 2->1 (типа 1533КП11 с 3им состоянием на выходе) и необходимых логических элементах.

Nз=Ni+3

В ответе привести: обоснование основных технических решений при построении заданного MUX, функциональную схему, условное графическое обозначение, таблицу состояний, краткое описание принципа действия предложенного MUX.

Решение.

Nб=2

Nз=12

nз=log212=4

4 ступень <- А3А2А1А0 -> 1 ступень

Третье состояние на выходе позволяет подключать ко входам следующей ступени параллельно несколько микросхем, из которых только одна в данный момент находится в рабочем состоянии. Один из способов построения нужной схемы – использование 6 мультиплексоров 2->1 с 3мя состояниями на выходе и 1го 3х разрядного дешифратора выходы которого подключены к входам, устанавливающим выходы в третье состояние.

Второй способ более экономный(рис. 1).

Рис.1

Первая ступень построена на основе селекторов-мультиплексоров с тремя состояниями на выходе. Для выбора текущего рабочего мультиплексора используется логический элемент 2И с инверторами на нужных входах. По этому в случае когда А3 и А2 – «1», на выходе всех трёх мультиплексоров будет Z-состояние и схема не будет работать.

Таблица состояний.

|

Х1 |

X2 |

X3 |

X4 |

X5 |

X6 |

X7 |

X8 |

X9 |

X10 |

X11 |

X12 |

Y |

A3 |

A2 |

A1 |

A0 |

|

0/1 |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

0/1 |

0 |

0 |

0 |

0 |

|

X |

0/1 |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

0/1 |

0 |

0 |

0 |

1 |

|

X |

X |

0/1 |

X |

X |

X |

X |

X |

X |

X |

X |

X |

0/1 |

0 |

0 |

1 |

0 |

|

X |

X |

X |

0/1 |

X |

X |

X |

X |

X |

X |

X |

X |

0/1 |

0 |

0 |

1 |

1 |

|

X |

X |

X |

X |

0/1 |

X |

X |

X |

X |

X |

X |

X |

0/1 |

0 |

1 |

0 |

0 |

|

X |

X |

X |

X |

X |

0/1 |

X |

X |

X |

X |

X |

X |

0/1 |

0 |

1 |

0 |

1 |

|

X |

X |

X |

X |

X |

X |

0/1 |

X |

X |

X |

X |

X |

0/1 |

0 |

1 |

1 |

0 |

|

X |

X |

X |

X |

X |

X |

X |

0/1 |

X |

X |

X |

X |

0/1 |

0 |

1 |

1 |

1 |

|

X |

X |

X |

X |

X |

X |

X |

X |

0/1 |

X |

X |

X |

0/1 |

1 |

0 |

0 |

0 |

|

X |

X |

X |

X |

X |

X |

X |

X |

X |

0/1 |

X |

X |

0/1 |

1 |

0 |

0 |

1 |

|

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

0/1 |

X |

0/1 |

1 |

0 |

1 |

0 |

|

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

0/1 |

0/1 |

1 |

0 |

1 |

1 |

|

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

0 |

1 |

1 |

0 |

0 |

|

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

0 |

1 |

1 |

0 |

1 |

|

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

0 |

1 |

1 |

1 |

0 |

|

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

X |

0 |

1 |

1 |

1 |

1 |

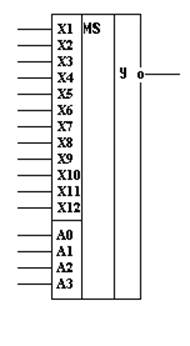

Условное графическое изображение полученного мультиплексора(рис.3).

Рис.3

Описание работы:

При подаче на адресные входы код требуемого входа, происходит следущее:

Двумя старшими битами выбирается одна из 3х микросхем, А1 задаёт какой из 2х (нулевой и первый каждой микросхемы ) мультиплексоров будет работать

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.