В зависимости от направления передачи информации они разделяются на параллельно-последовательные и последовательно-параллельные. Основными элементами этих преобразователей являются регистровые схемы.

Принцип параллельно-последовательного преобразования сводится к одновременной подаче на входы регистра всех элементов кода и последующего поочерёдного считывания каждого элемента. Управление параллельной записью кода в регистр осуществляется группой элементов И – НЕ, кратных разрядности кода. Система связей между ячейками регистра, а также последовательность импульсов считывания таковы, что на выходе последней ячейки с заданной частотой появляется последовательно весь код.

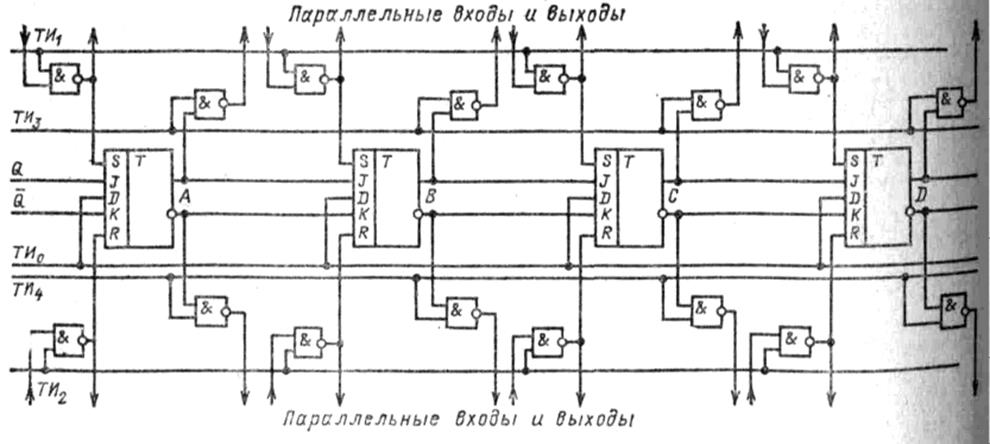

Принцип последовательно-параллельного преобразования кода заключается в последовательной записи по единственной входной шине поочерёдно во все ячейки регистра синхронно с тактовыми импульсами ТИ требуемого кода и в одновременном считывании из этих ячеек через группу элементов И – НЕ на соответствующие шины всей комбинации (рис.6).

Рис.6. Преобразователь кода

Преобразователи кодов указанного типа находят широкое применение в устройствах связи микропроцессорных средств с отдалёнными объектами по двухпроводным каналам. На выходе передатчика такого устройства устанавливается преобразователь параллельного кода в последовательный; на входе приёмника – преобразователь последовательного кода в параллельный.

- преобразователи, у которых элементы выходного кода содержат все элементы

входного кода и дополнительные корректирующие элементы;

Преобразователи кодов второго типа, ориентированные на работу с систематическими кодами, реализуются с помощью сумматоров по модулю и рекуррентных регистров и используются для обнаружения и исправления определённого числа ошибок. Указанные корректирующие коды образуются добавлением некоторого числа контрольных элементов к информационным элементам входного кода.

Преобразователь кода, например, с чётным числом единиц при m-разрядном входном коде содержит m+1-разрядный регистр и сумматор по модулю два, выход которого соединён с m+1-й ячейкой регистра, а все входы – с остальными ячейками. При нечётном числе единиц во входном коде, на выходе сумматора формируется единица дополняющая выходной код в регистре до чётности, при чётном – в последнем разряде выходного кода – нуль.

Преобразователь кода Хемминга содержит информационный регистр сдвига и ряд сумматоров по модулю два, формирующих по определённому алгоритму дополнительные разряды. Например, для пятиэлементного кода на входе такой преобразователь должен иметь девятиразрядный регистр сдвига и три сумматора по модулю два. Все выходные девятиэлементные коды, полученные по алгоритму Хемминга, отличаются один от другого минимум тремя разрядами. Использование такого преобразователя кода обеспечивает исправление одиночных и обнаружение одиночных и двойных ошибок. Указанный преобразователь находит всё более широкое применение при построении арифметических устройств, оперативной памяти микропроцессорных управляющих вычислительных комплексов.

- преобразователи, у которых элементы выходного кода в явном виде не

соответствуют элементам входного кода.

К преобразователям кодов третьего типа относятся устройства, использующие комбинационные схемы. По этому методу процесс преобразования разделяется на два этапа: во-первых, все элементы m-разрядного входного кода преобразуется в промежуточный позиционный N-разрядный код и, во-вторых, промежуточный код преобразуется в требуемый M-разрядный. Первый этап процесса реализуется дешифратором, второй – шифратором.

2.1ДЕШИФРАТОР

Дешифратором называется преобразователь кода, в котором при поступлении на вход определённого символа двоичного кода возбуждается один из выходов.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.