|

xi |

yi |

Pi |

Si |

Pi+1 |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

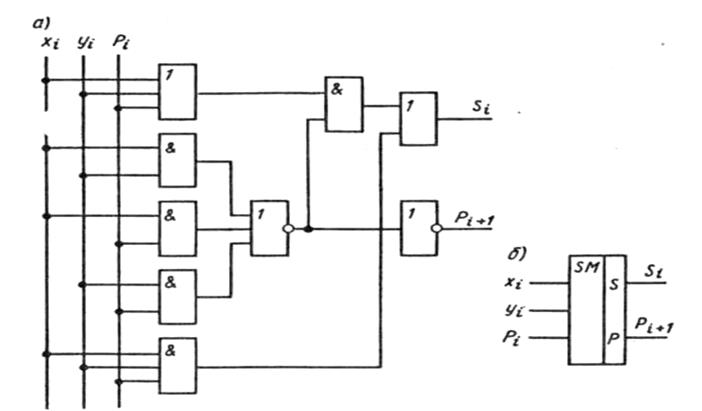

В соответствии с этой таблицей работа полного сумматора описывается следующими логическими выражениями:

Si=![]() V(

V(![]() V

V ![]() V

V![]() )(

)(![]() );

);

Pi+1=![]() V

V![]() V

V![]() ,

,

которым соответствуют функциональная схема и условное обозначение сумматора, приведенные на рис.2, а, б.

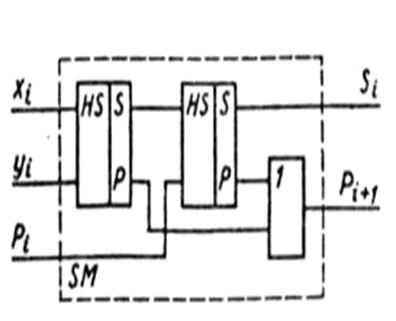

Комбинационный сумматор можно реализовать также с использованием двух полусумматоров и логического элемента ИЛИ, как показано на рис.3.

Суммирование многоразрядных кодов осуществляется с помощью одноразрядных сумматоров. При этом в зависимости от характера ввода-вывода кодов и организации переносов многоразрядные сумматоры бывают последовательного и параллельного принципа действия.

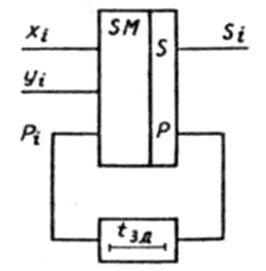

В последовательном сумматоре (рис.4) сложение кодов осуществляется поразрядно начиная с младшего разряда с помощью комбинационного сумматора на три входа.

Образующийся в данном разряде перенос Pi+1 задерживается на время tзд и поступает на вход Piсумматора в момент поступления следующего разряда слагаемых. Таким образом, последовательно разряд за разрядом производится сложение кодов чисел. Достоинством последовательного сумматора является простота аппаратурной реализации, а недостатком – достаточно большое время суммирования.

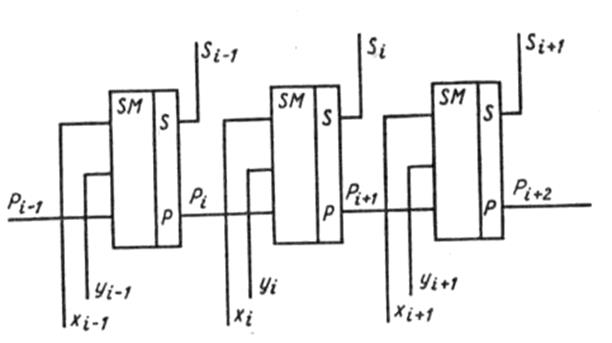

В параллельном сумматоре (рис.5) достигается более высокое быстродействие.

Суммируемые коды поступают на входы сумматора одновременно по всем разрядам. Для этого в каждом разряде используется комбинационный сумматор на три входа, на выходах которого образуется значения суммы Siданного разряда и переноса Pi+1 в старший разряд. В процессе распространения сигнала переноса устанавливается окончательное значение суммы в каждом разряде. Очевидно, что в течении этого времени на входах сумматора присутствуют сигналы xi , yi соответствующие суммируемым кодам. Максимальное по времени суммирование получается в том случае, когда перенос, возникший в первом разряде, распространяется по всем разрядам ( например, при сложении кодов 11…11 и 00…01). В параллельных сумматорах обычно применяются различные способы ускорения переноса (параллельный перенос, групповой и т.п.)

2.ПРЕОБРАЗОВАТЕЛИ КОДОВ

В процессе обработки информационных потоков в системах автоматики и вычислительной техники имеет место работа с различными комбинациями дискретных сигналов – с кодами. Кодом называется определённая совокупность электрических сигналов и пауз, соответствующая какому-либо информационному символу.

Преобразователем кодов называется устройство для автоматического изменения по заданному алгоритму соответствия между входными и выходными кодами без изменения их смыслового содержания.

В зависимости от входных и выходных кодов преобразователи могут быть классифицированы по различным признакам – по числу символов алфавита, по виду электрического сигнала, по способу передачи элементарных сигналов, по степени достоверности и т.п. Рассмотрим варианты построения преобразователей кодов, отличающиеся степенью соответствия выходных кодовых комбинаций входным. Будем различать следующие разновидности преобразователей:

- преобразователи, у которых элементы выходного кода в явном виде соответствуют одноимённым элементам входного кода.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.