Таблица 2. Логическая таблица режимов работы шифратора К555ИВ3.

|

Входы |

Выходы |

Примечания |

|||||||||||

|

I1 |

I2 |

I3 |

I4 |

I5 |

I6 |

I7 |

I8 |

I9 |

Y3 |

Y2 |

Y1 |

Y0 |

|

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

Если ни один из входов не активен – на выходах напряжения высокого уровня (High - H). |

|

x |

x |

x |

x |

x |

x |

x |

x |

0 |

0 |

1 |

1 |

0 |

В зависимости от того, на какой из входов подаётся низкий уровень (т.е. 0 или L, которые являются активными уровнями), генерировать на выходе двоично-десятичное значение наиболее приоритетного активного входа. Вход I9 имеет наивысший приоритет, вход I1 – низший. |

|

x |

x |

x |

x |

x |

x |

x |

0 |

1 |

0 |

1 |

1 |

1 |

|

|

x |

x |

x |

x |

x |

x |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

|

|

x |

x |

x |

x |

x |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

|

|

x |

x |

x |

x |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

|

|

x |

x |

x |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

|

|

x |

x |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

|

|

x |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

|

|

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|

Для клеток, где указан символ «x», значение соответствующих сигналов на входах указывать необязательно, т.к. активен какой-либо из более приоритетных входов. Поэтому вместо «x» можно подставлять как 1, так и 0.

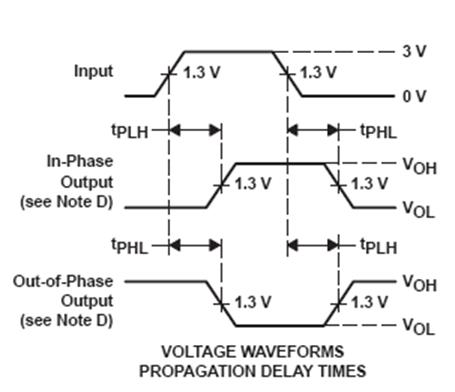

Значения задержек переключений кодера взяты из фирменной документации Texas Instruments для элемента 74LS147 (см. Приложение 1), а также из источника [8] (см. Приложение 2).

Таблица 3. Реальные задержки кодера К555ИВ3.

|

Обозна-чение |

От входа |

До выхода |

Форма выходного сигнала относительно входного |

Величина номинальной задержки, нс |

Описание |

|

tPLH |

От любого входа до любого выхода |

В фазе (In-phase output) |

12 |

Переключение выходного сигнала из 0 в 1, если это обусловлено изменением входного сигнала также с 0 на 1. |

|

|

tPHL |

12 |

Переключение выходного сигнала из 1 в 0, если это обусловлено изменением входного сигнала также с 1 на 0. |

|||

|

tPLH |

От любого входа до любого выхода |

В противофазе (Out-of-phase output) |

21 |

Переключение выходного сигнала из 0 в 1, если это обусловлено изменением входного сигнала с 1 на 0. |

|

|

tPHL |

15 |

Переключение выходного сигнала из 1 в 0, если это обусловлено изменением входного сигнала с 0 на 1. |

|||

Наверное, стоит объяснить, что такое переключение в фазе и противофазе: если входной сигнал переключается с низкого уровня на высокий или наоборот, а выходной при этом повторяет его форму (т.е. тоже переключается с низкого уровня на высокий или наоборот) – то это переключение выходного сигнала в фазе относительно входного. А если вход переключается с L на H (с H на L), а выход – с H на L (с L на H), то это – переключение в противофазе:

Рис.2. Параметры tPLH и tPHL (см. также Приложение 1).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.