Предельная

частота работы – такая частота переключения данных на входах, при которой

элемент ещё выдаёт правильный результат. Теоретически предельную частоту работу

можно оценить как  , где Тзад –

максимальное значение задержки какого-либо элемента по пути прохождения

сигнала.

, где Тзад –

максимальное значение задержки какого-либо элемента по пути прохождения

сигнала.

1). Для

макромодели в качестве Тзад следует взять значение 21 нс, это

максимальная задержка переключения какого-либо из входов. Получим:  .

.

2). Для

элемента со схемой замещения принимаем Тзад равным 9нс (максимальная

задержка для элемента 2ИЛИ). В результате:  .

.

Стоит добавить, что полученные частоты рассчитаны на наибольшую задержку (для режима противофазы). Т.о., если «держать» активным на входах кодера только один сигнал, то предельная частота работы для элемента, поддерживаемого макромоделью, составит 41,6 МГц, а для элемента, поддерживаемого схемой замещения – все 250 Мгц!

Проверим это.

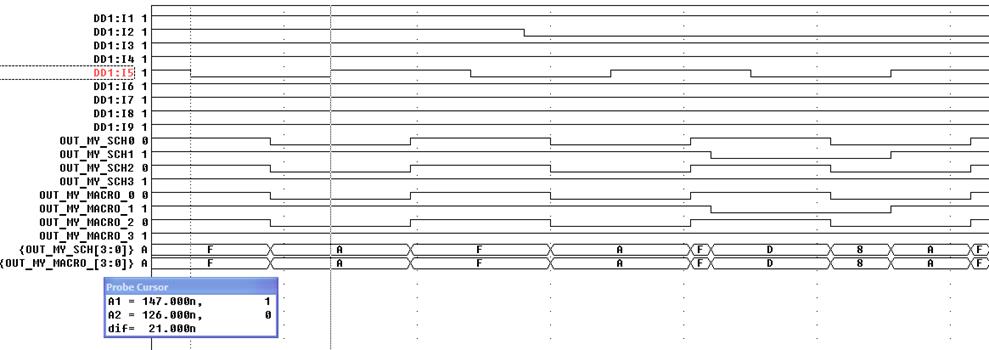

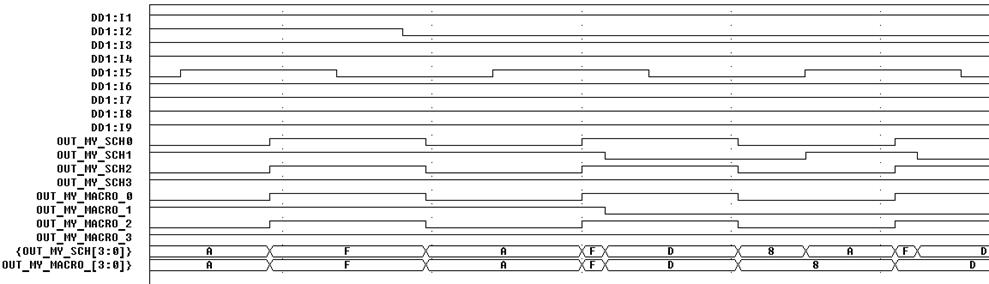

Рис. 13. Работа цифровых узлов на частоте переключения входа I5 23.8 МГц.

По диаграмме видно, что элемент, поддерживаемый макромоделью «держит» частоту 23.8 МГц, т.к. значения на его выходах идентичны элементу на схеме замещения, для которого такая частота – не предельная.

Рис. 14. Работа цифровых узлов на частоте переключения входа I5 23.9 МГц.

А вот в этом случае элемент на макромодели работает неправильно. До переключения сигнала I2 в активный уровень всё было в порядке, а после его переключения на активный уровень при подаче и снятии активного уровня на вход I5 видно различие в работе элементов: на выходах узла с макромоделью не наблюдается комбинация А (1010), что соответствует приходу активного уровня на более приоритетный вход I5. Следовательно, на такой частоте элемент, поддерживаемый макромоделью, работать корректно не может.

Ниже приведён тест компонента, поддерживаемого схемой замещения:

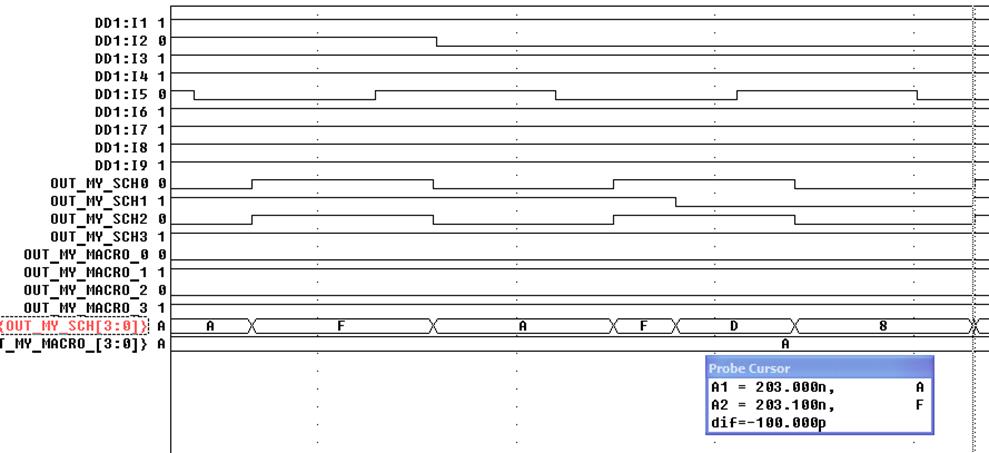

Рис. 15. Работа цифровых узлов на частоте переключения входа I5 55 МГц.

Конечно, не очень удачный опыт, зато он хорошо показывает: схема способна работать на частоте 55МГц, однако нужная комбинация – 1010 (А) появляется на выходах микросхемы лишь на 0.1 нс. При увеличении частоты схема «отказывается» выдавать данную комбинацию на выход, т.е. начинает работать неправильно. Также стоит отметить, что элемент на макромодели на такой частоте не переключается вовсе.

Приводить тест определения предельных частот работы узлов для случая, когда активен только один из их входов, я не буду, т.к. и это только увеличит объём пояснительной записки. Замечу, однако, что значения, полученные для такого случая выше, достоверны.

Итак, подведём итог выполнению данного пункта в виде некоторой «документации» к шифратору К555ИВ3:

Таблица 4. Предельные скоростные характеристики К555ИВ3.

|

Возможное количество одновременно активных входов |

Предельное значение частоты, МГц |

|

|

Для макромодели |

Для схемы замещения |

|

|

1 |

23.8 |

250 |

|

Более 1 |

41.6 |

55 |

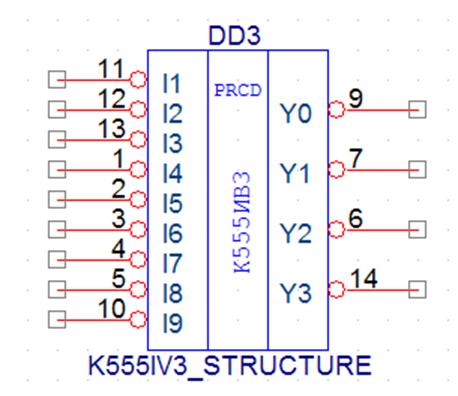

Рис. 16. Условное графическое обозначение проектируемого символа в пакете OrCad 9.1.

Рис. 17. Схема замещения элемента К555ИВ3 в пакете OrCad 9.1 .

Итак, элемент со схемой замещения получен. Сама схема смотрится, конечно, не так «эффектно», как в DesignLab’е из-за некоторой «несвязности». Однако схема нарисована не специально, она и так с трудом уместилась на одной странице, а разбивать её на несколько страниц не было смысла – всё равно получилось бы нечто подобное.

Не будем по отдельности тестировать элементы, поддерживаемые схемой замещения и VHDL-моделью – сделаем новый символ, подключим к нему VHDL-модель и приведём результаты моделирования на одной ВД.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.