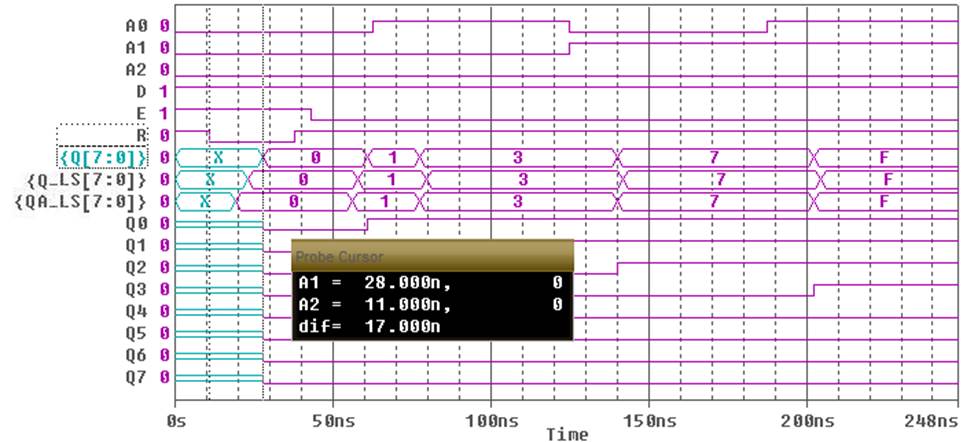

Рис.8. Задержка распространения сигнала от входа R до выхода Q при переключении его из 1 в 0 (17 нс).

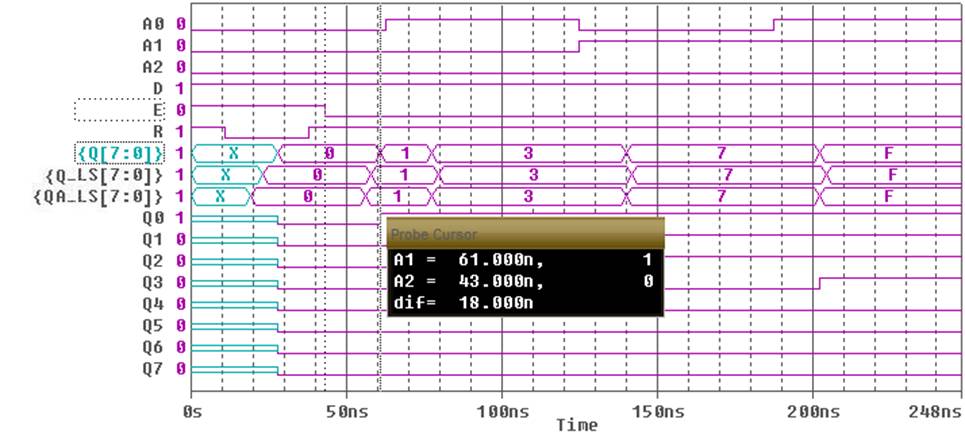

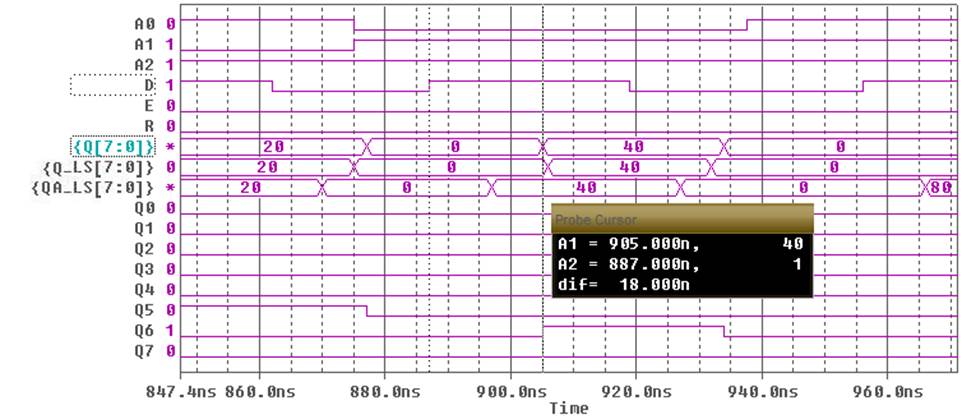

Рис.9. Задержка распространения сигнала от входа E до выхода Q при переключении его из 1 в 0 (18 нс).

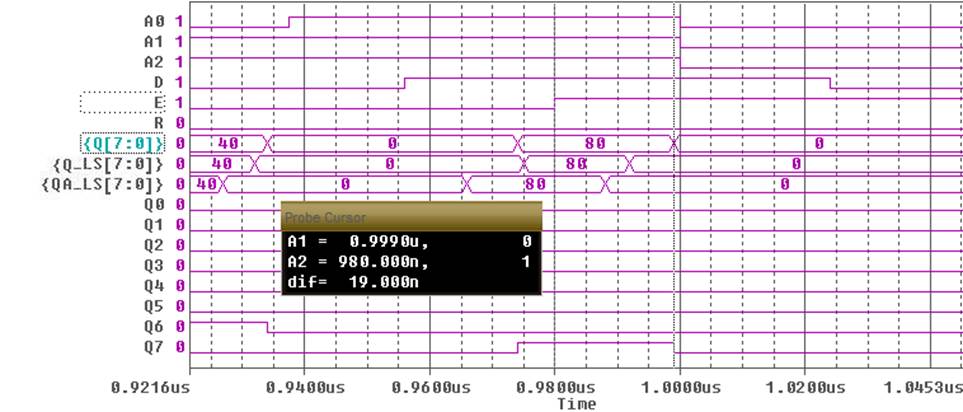

Рис.10. Задержка распространения сигнала от входа E до выхода Q при переключении его из 0 в 1 (19 нс).

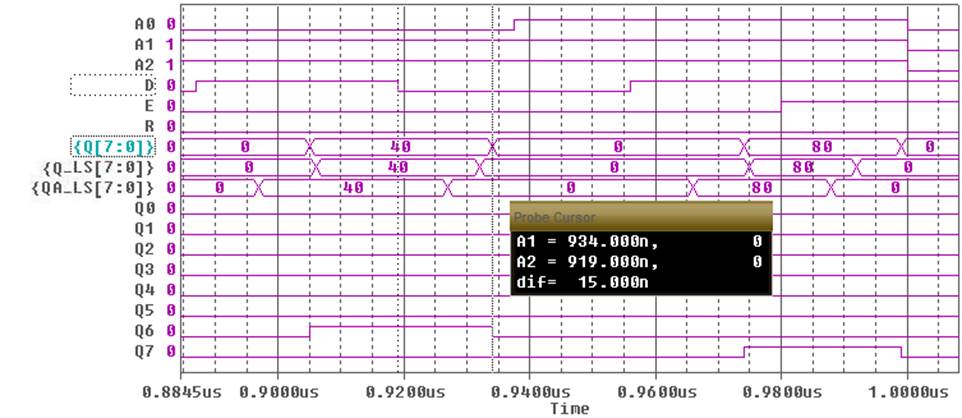

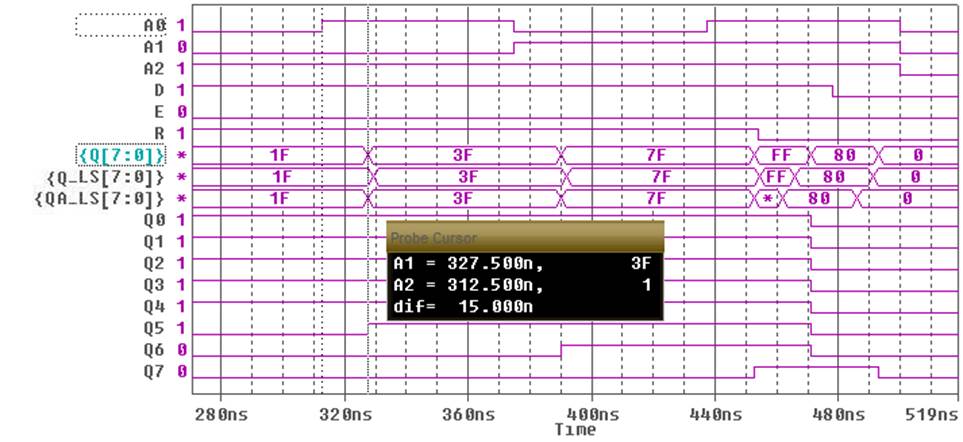

Рис.11. Задержка распространения сигнала от входа D до выхода Q при переключении его из 1 в 0 (15 нс).

Рис.12. Задержка распространения сигнала от входа D до выхода Q при переключении его из 0 в 1 (18 нс).

Рис.13. Задержка распространения сигнала от входа A до выхода Q при переключении его из 1 в 0 (15 нс).

Временные диаграммы работы узла были построены таким образом, чтобы можно было измерить задержки во всех возможных ситуациях. Все задержки распространения сигнала совпадают со значениями из таблицы 3 (стр. 6), что подтверждает верное функционирование узла.

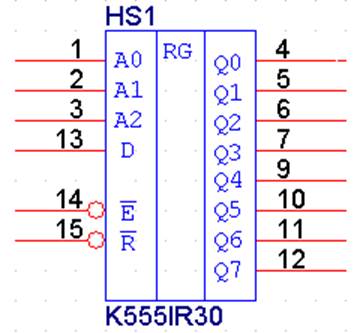

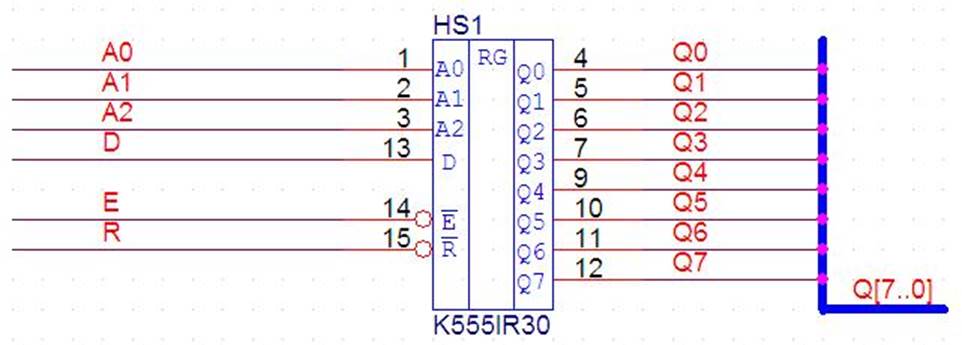

Условное графическое обозначение проектируемого узла в виде иерархического символа в PCB Simulate – проекте представлено на Рис. 14.

Рис.14. УГО моделируемого узла К555ИР30 в виде иерархического символа.

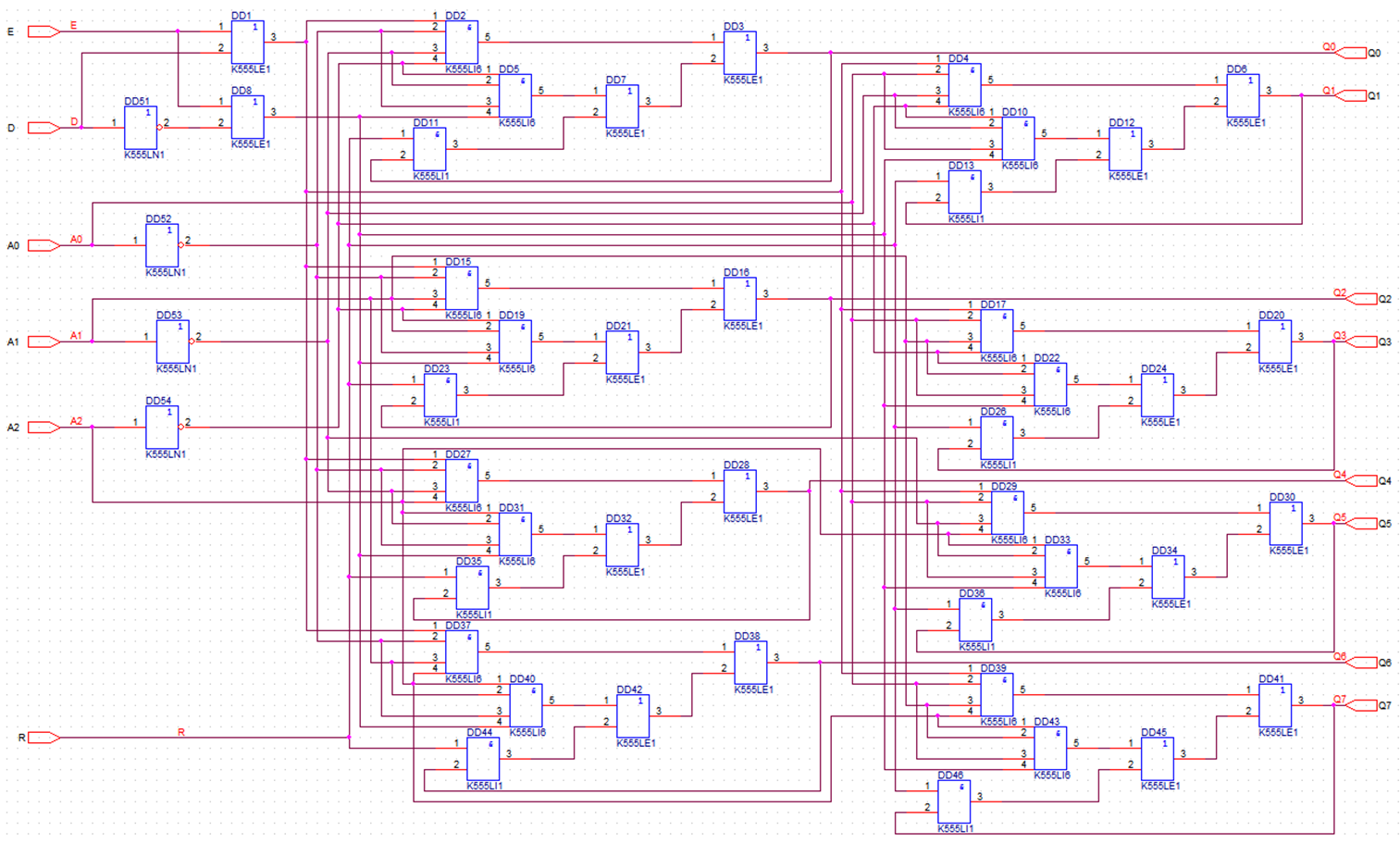

Основой для проектирования схемы замещения стали логические элементы 2ИЛИ, 2И, 4И и НЕ. Ниже приведены VHDL-модели для данных элементов (листинг 2). Схема замещения построена на основе созданных в библиотеке «K555IR30.olb» элементов (рис. 15).

Листинг 2.VHDL модели используемых элементов.

*Элемент НЕ*

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE work.orcad_prims.all;

ENTITY \K555LN1\ IS PORT(

IN1 : IN std_logic;

OUT1 : OUT std_logic;

VCC : IN std_logic;

GND : IN std_logic);

END \K555LN1\;

ARCHITECTURE model OF \K555LN1\ IS

BEGIN

OUT1 <= not ( IN1 );

END model;

*Элемент 2И*

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE work.orcad_prims.all;

ENTITY \K555LI1\ IS PORT(

IN1 : IN std_logic;

IN2 : IN std_logic;

OUT1 : OUT std_logic;

VCC : IN std_logic;

GND : IN std_logic);

END \K555LI1\;

ARCHITECTURE model OF \K555LI1\ IS

BEGIN

OUT1 <='1' after 0 ns when (IN1 and IN2)='1'

else '0' after 10 ns;

END model;

*Элемент 4И*

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE work.orcad_prims.all;

ENTITY \K555LI6\ IS PORT(

IN1 : IN std_logic;

IN2 : IN std_logic;

IN3 : IN std_logic;

IN4 : IN std_logic;

OUT1 : OUT std_logic;

VCC : IN std_logic;

GND : IN std_logic);

END \K555LI6\;

ARCHITECTURE model OF \K555LI6\ IS

BEGIN

BEGIN

OUT1 <=( IN1 and IN2 and IN3 and IN4 ) after 8 ns;

END model;

* Элемент 2 ИЛИ*

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE work.orcad_prims.all;

ENTITY \K555LE1\ IS PORT(

IN1 : IN std_logic;

IN2 : IN std_logic;

OUT1 : OUT std_logic;

VCC : IN std_logic;

GND : IN std_logic);

END \K555LE1\;

ARCHITECTURE model OF \K555LE1\ IS

BEGIN

OUT1 <= '1' after 3 ns when ( IN1 or IN2 )='0'

else '0' after 4 ns;

END model;

Рис. 15. Схема замещения проектируемого символа HS1.

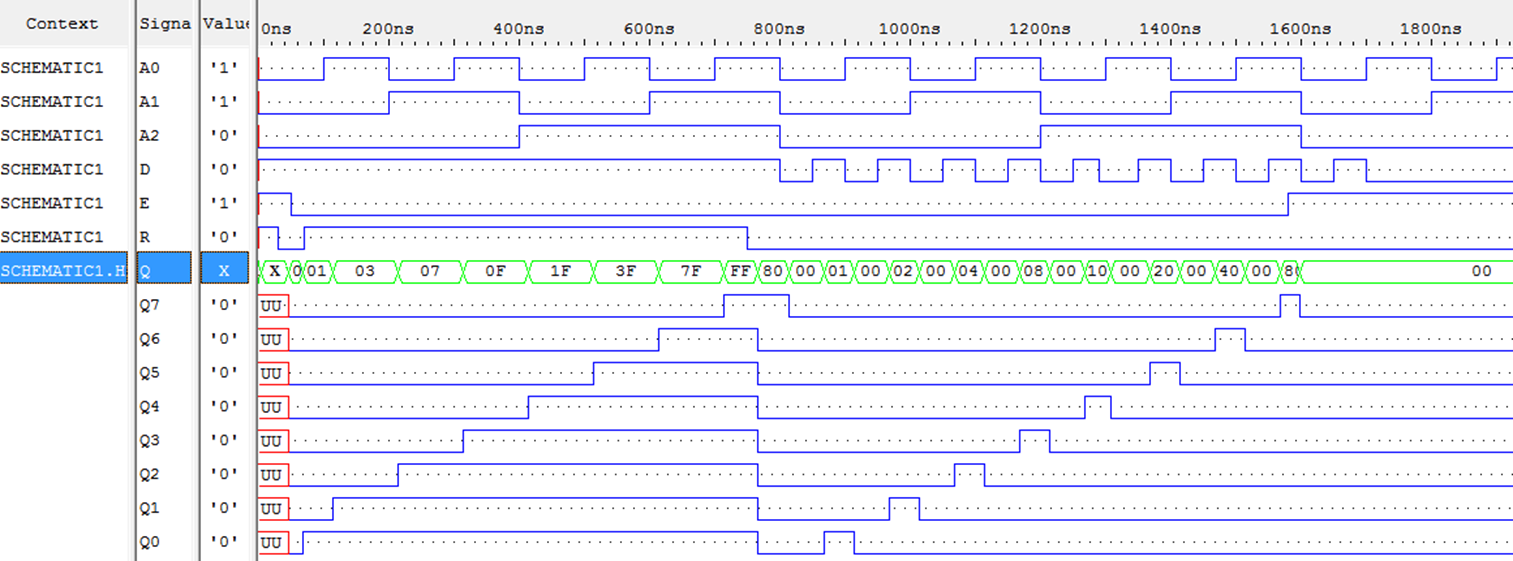

Верификация произведена на основе использования узла, созданного в SPICE – проекте и получившегося иерархического символа в PCB Simulate – проекте (рис.16).

Рис.16. Схема использования иерархического символа, созданного в PCB Simulate – проекте.

Режимы работы элемента в PCB Simulate–проекте (Рис. 17) полностью соответствуют режимам работы в SPICE – проекте.

Рис.17. Временная диаграмма работы проектируемого узла

Полученная временная диаграмма отражает все режимы работы проектируемого узла. Выполнив сравнение с SPICE – проектом (рис.7), можно сделать вывод, что микросхемы функционируют верно.

Для того чтобы убедиться в том что задержки подобраны верно, рассмотрены временнее диаграммы моделируемого узла (рис.18-23). Задержки совпадают с полученными при проектировании узла в SPICE – проекте.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.