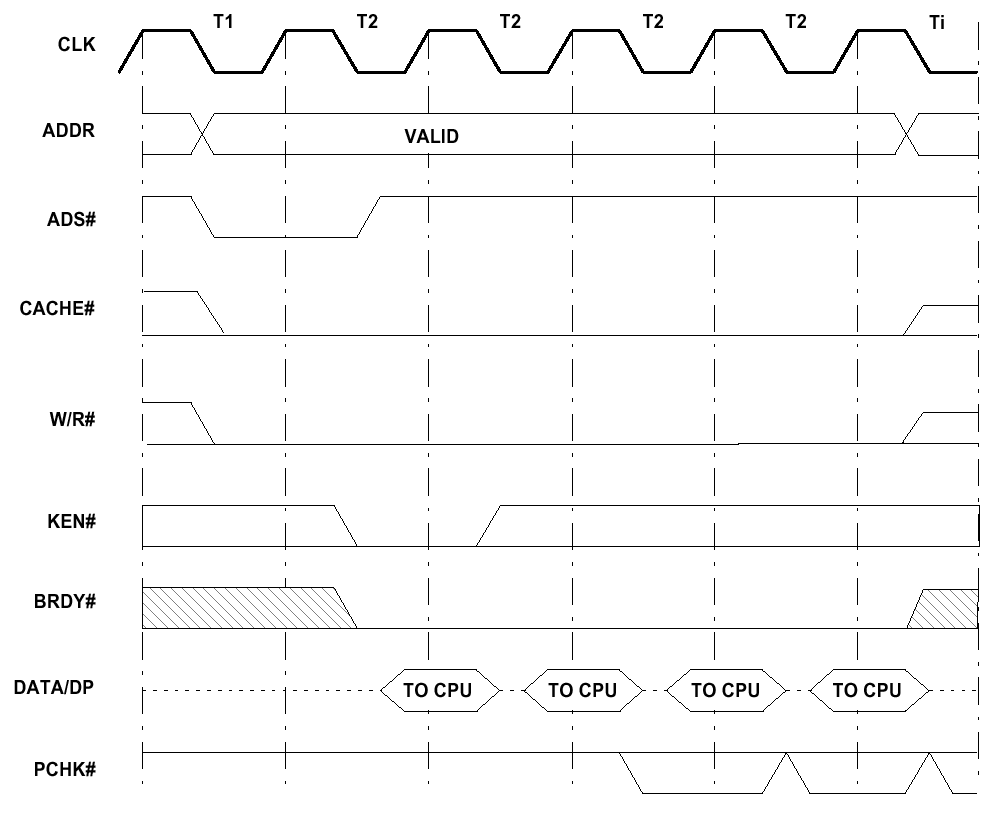

Подобный пакетный цикл впервые был реализован в канале процессора i486, с целью ускорить процесс передачи кэш-строки между ОЗУ и кэш-памятью. Канал процессора 486 имеет 32-разрядные шины адреса и данных. Строка кэш-памяти первого уровня в i486 находится на кристалле и имеет длину 16 байтов (4 длинных слова). Таким образом, для передачи содержимого кэш-строки требуется четыре канальных цикла.

Пакетный цикл процессоров 486+ имеет одну адресную фазу и четыре следующих подряд фазы данных, в которых передаются четыре 32-разрядных слова, расположенные в памяти по идущим подряд адресам. Пассивное устройство (схемотехника управления памятью) должно быть в состоянии, после получения адреса для первого слова, само сформировать адреса для последующих трех слов.

Представленная далее временная диаграмма пакетного цикла заимствована из документа фирмы Intel Pentium® Processor Family Developer’s Manual Volume 1: Pentium® Processors.

В разделе 6.3.2. Burst Cycles (стр. 6-14 по нумерации документа, стр. 177 по порядку от начала) подробно описаны разные виды пакетных циклов.

|

|

|

|

|

|

Рис. Пакетный цикл на магистрали процессоров 486+

В ходе этого канального цикла процессор обменивается информацией с контроллером прерываний и получает от него информацию о номере вектора, соответствующего источнику запроса.

(Извините, подраздел в процессе…..)

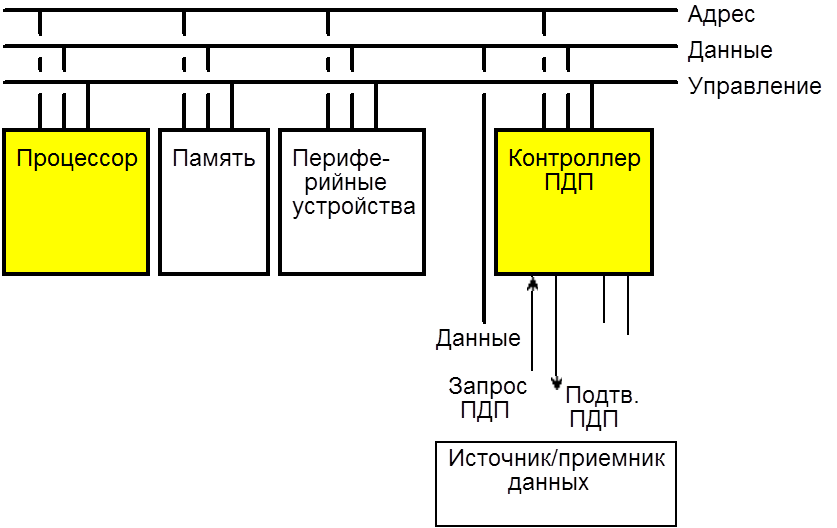

Сущность ПДП состоит в том, что в микропроцессорной системе имеются кроме процессора другие устройства: способные быть активными (bus masters).

Рис.6. Структура системы с несколькими задатчиками магистрали

Такими свойствами могут обладать контроллеры дисков, видеобластеры (устройства ввода изображения) и др. Обычный режим их работы состоит в том: что они записывают или считывают большие обьемы данных, непостредственно взаимодействуя через канал с памятью (отсюда и название -ПДП). Собственно передача данных из/в память происходит с использованием канальных циклов передачи данных, с той разницей, что управление каналом (формирование адресов и управляющих сигналов) осуществляет не процессор а ПДП-устройство. Однако для перехода в такой режим (т.е. для передачи управления каналом от одного задатчика к другому) на канале предусматривается специальная процедура и имеются в составе шины управления специальные управляющие сигналы.

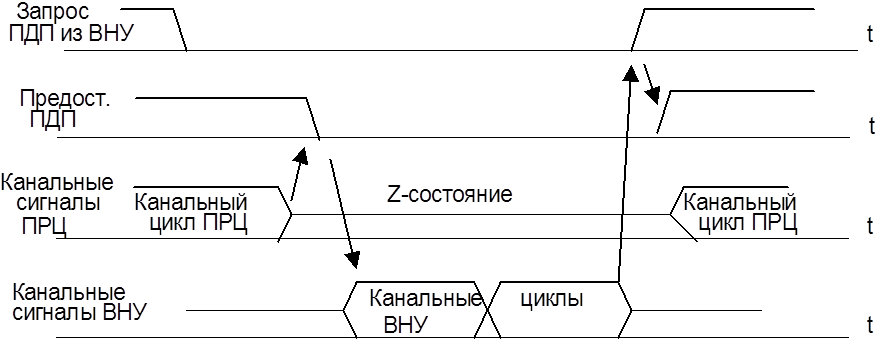

Простейший случай, когда в системе имеется только два задатчика шины, иллюстрирует рис.7.

Рис. 7 Типовая временная диаграмма предоставления прямого доступа

Процедура передачи данных в режиме ПДП состоит в следующем.

Запрос DREQ (Dma REQuest) на начало передачи поступает в контроллер ПДП в виде электрического сигнала из внешнего устройства.

КПДП посылает в процессор запрос канала HOLD

Процессор заканчивает текущий канальный цикл и предоставляет канал, о чем сообщает сигналом HLDA (предоставление канала).

КПДП генерирует канальные циклы (т.е. нужные адреса и последовательности управляющих сигналов), в которых между памятью и внешним устройством происходит обмен байтами (или словами).

Перед началом обмена программа должна указать контроллеру

ПДП:

- начальный адрес массива в памяти, куда (или откуда) будет передача

- направление передачи (в память или из нее)

- количество байтов (или слов), которые надо передать

- как реагировать на сигнал запроса......

и некоторые другие условия (см. далее описание КПДП для PC-совместимых

компьютеров).

Начало передачи может происходить не только по внешнему сигналу, но и по команде (устанавливающей нужный бит в нужном порте) - по аналогии с прерыванием.

В более сложном случае, когда в системе есть несколько (более двух) задатчиков, необходимо иметь специальное устройство - арбитр шины, которое должно управлять ситуациями, когда одновременно более чем один задатчик запрашивает управление шиной.

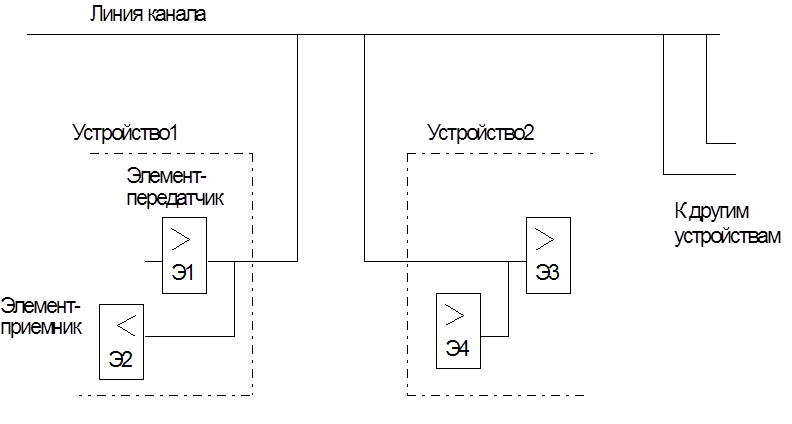

Для обеспечения быстрого перезаряда паразитных емкостей линий связи между логическими элементами в их выходных каскадах используют комплементарные инверторы.

. На рис.8 изображена структура, обеспечивающая двунаправленную связь по линии канала.

Рис. 8 Структура двунаправленной связи по линии канала

При передаче от Устройства1 к Устройству2 работают выход Э1 и вход Э3. При обратной передаче работают выход Э4 и вход Э2. При этом оказывается, что два выхода: Э1 и Э4 соединены вместе. Это может привести к электрическому конфликту, если они оба попытаются одновременно передавать разные значения логической переменной.

Это комплементарные (биполярные или МОП) сложные инверторы, в которых сущестует третье (отключенное) Z-состояние, когда оба выходных транзистора сложного инвертора нахоятся в непроводящем состоянии. У таких элементов есть дополнительный управляющий вход включения Z-состояния, часто обозначаемый как OE (Output Enable). При нормальном функционировании в каждый момент времени только один выход должен передавать (т.е. находиться не в Z-состоянии) - и это должен обеспечить разработчик устройства правильным формированием сигналов на входах OE разных микросхем, подключенных к одной и той же линии канала.

Это элементы, выходные каскады которых не содержат

в выходном каскаде "верхнего" (pull-up) транзистора. Такие выходы

можно соединять к одной линии, не опасаясь электрического конфликта, при этом

происходит обьединение выходных сигналов в соответствии с фугкцией

"логического ИЛИ" для сигналов низкого уровня. Поэтому подобное

соединение на схемотехническом жаргоне называют "монтажным ИЛИ"

(wired OR).

Достоинство - отсутствие электрического конфликта сопровождается

недостатком: для обеспечения на такой линии сигнала "логической

единицы" (high) необходимо между такой линией и источником питания

включать внешний резистор. Иногда такой резистор выполняется непосредственно на

микросхеме. При малой величине проводимости этого резистора увеличивается время

перезаряда паразитной емкости линии (т.е. уменьшается быстродействие), а при

повышении проводимости - растет потребляемая мощность.

В некоторых микросхемах применяют комбинированный вариант, когда

верхний резистор комплементарного инвертора присутствует, но открывается

импульсно, лишь на короткое время при переключении линии из Low в High,

обеспечивая быстрый перезаряд емкости линии и в то же время отсутствие

электрического конфликта в статическом состоянии. Так сделано например в

выходных каскадах портов контроллера i8051.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.