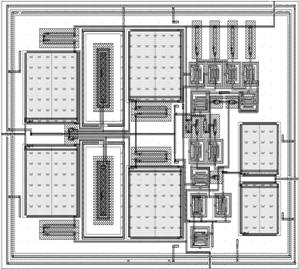

Ниже

представлена топология базовой ячейки. Размеры ячейки составляют 155 х 108 мкм.

Рис. 1. – Топология базовой ячейки умножителя с RF-транзисторами

Общая методика проведения экспериментальных исследований доработанной ячейки умножителя.

Экспериментальные исследования проводятся с использованием программы аналогового моделирования Spectre пакета САПР Cadence в соответствии с [6]. Подготовка к проведению экспериментальных исследований включает в себя следующие этапы:

- создание общей модели электрической схемы;

- создание общей модели экстрактированной из топологии схемы;

-подключение моделей элементов к программе моделирования Spectre;

- задание типа анализа и времени моделирования;

- задание входных воздействий на входах схемы;

- определение способа и списка просмотра сигналов.

Программа проведения эксперимента:

1. Оценка широкополосности схемы базовой ячейки;

2. Моделирование топологии ячейки при работе ее на частотах, определенных при исследовании электрической схемы, анализ спектра выходного сигнала;

3. Оценка влияния изменения температуры на работу топологии ячейки.

4. Оценка влияния возможного изменения параметров структурных элементов топологии при изготовлении схемы на работу ячейки.

По требованию [7] электронная структура изделий описана с использованием языка описания моделей данных, регламентированного ИСО 10303-11. Модели построены на основе принципов описания элементов и приборов схемы и топологии, подробно рассмотренных в [5], [6] и [8].

Моделирование производится в аналоговом режиме с максимальной точностью. Точность моделирования при этом полностью определяется качеством характеризации моделей библиотечных элементов базовой библиотеки.

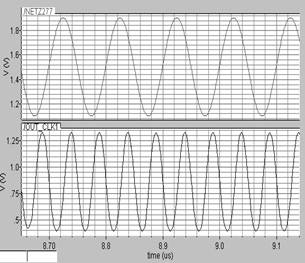

Оценка широкополосности базовой ячейки умножителя. Нагрузочные резисторы имеют сопротивления 3,8 кОм. На вход схемы подается синусоида с частотой 10 МГц – 250 МГц с амплитудой 0,5 В. На рисунках 2 и 3 представлены временные диаграммы работы ячейки при частотах входного сигнала 10 МГц и 100 МГЦ соответственно.

Рис. 2. Временная диаграмма работы схемы ячейки умножителя при частоте входного сигнала 10 МГц.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.