запрещает запись в страницы, помеченные как «только для чтения» на всех уровнях привилегий (при WP=0 – защита распространяется только на уровень 3).

· NE - включает режим, в котором ошибки FPU вызывают исключение #MF, а не IRQ13.

· ET - использовался только на 80386DX и указывал, что FPU присутствует.

· TS - устанавливается процессором после переключения задачи. При дальнейшем использовании FPU вызывает его предварительную очистку.

· EM - эмуляция сопроцессора.

· MP - управляет режимом выполнения команды WAIT. Должен быть установлен для совместимости с программами, написанными для 80286 и 80386, использующими эту команду.

· PE - установлен в 1 при работе в защищенном режиме.

CR1 – зарезервирован.

CR2 – регистр адреса ошибки страницы. Если произошло исключение #PF, из этого регистра можно получить линейный адрес, обращение к которому вызвало исключение.

CR3 (PDBR) – регистр основной таблицы страниц:

|

31…11 |

10…5 |

4 |

3 |

2…0 |

|

PR4: PAE =0 |

PAE=1 |

Бит запрещения кэширования страниц |

Бит сквозной записи страниц |

|

|

20(27)-битный физический адрес начала каталога страниц |

||||

CR4 – только для процессоров Pentium, управляет новыми возможностями процессоров.

DR7 – регистр управления отладкой

DR6 – регистр состояния отладки

DR4 иDR5 – зарезервированы

DR3 – DR0 – содержат 32-битные адреса четырех возможных точек останова до доступу к памяти.

Впервые этот режим появился в микропроцессоре i80286. Именно этот режим позволяет полностью использовать все возможности представляемые современными микропроцессорами. Все многозадачные операционные современные системы (такие как Microsoft Windows, Unix) работают в этом режиме.

Основная трудность, с которой сталкивается программист, изучающий защищённый режим - это сложная схема преобразования адресов.

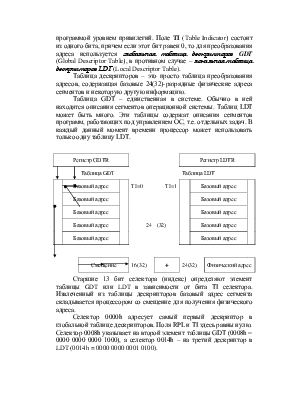

В защищённом режиме, также как и в реальном, существуют понятия логического и физического адреса. Логический адрес в защищённом режиме (иногда используется термин "виртуальный адрес") состоит из двух 16-разрядных компонент - селектора и смещения. Селектор записывается в те же сегментные регистры, что и сегментный адрес в реальном режиме. Однако преобразование логического адреса в физический выполняется не простым сложением со сдвигом, а при помощи специальных таблиц преобразования адресов.

В первом приближении можно считать, что для процессора i80286 селектор является индексом в таблице дескрипторов, содержащей базовые 24(32)-разрядные физические адреса сегментов. В процессе преобразования логического адреса в физический процессор прибавляет к базовому 24(32)-разрядному адресу 16(32)-разрядное смещение, т.е. вторую компоненту логического адреса.

|

|

|

|

Такая схема формирования физического адреса позволяет непосредственно адресовать 16 Мбайт памяти с помощью 16 разрядных компонент логического адреса.

На самом деле не все 16 бит селектора используются для индексации по таблице базовых адресов. В качестве индекса выступают лишь старшие 13 бит. Два младших бита используются (0 и 1) используются системой защиты памяти, а бит 2 позволяет выбрать для преобразования адреса один из двух типов таблиц преобразования адресов.

|

Селектор |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Индекс |

TI |

RPL |

||||||||||||||

На этом рисунке два младших бита обозначены как RPL (Requested Privilege Level). Это поля является запрошенным программой уровнем привилегий. Поле TI (Table Indicator) состоит из одного бита, причем если этот бит равен 0, то для преобразования адреса используется глобальная таблица дескрипторов GDT (Global Descriptor Table), в противном случае – локальная таблица дескрипторов LDT (Local Descriptor Table).

Таблица дескрипторов – это просто таблица преобразования адресов, содержащая базовые 24(32)-разрядные физические адреса сегментов и некоторую другую информацию.

Таблица GDT – единственная в системе. Обычно в ней находятся описания сегментов операционной системы. Таблиц LDT может быть много. Эти таблицы содержат описания сегментов программ, работающих под управлением ОС, т.е. отдельных задач. В каждый данный момент времени процессор может использовать только одну таблицу LDT.

|

Регистр GDTR |

Регистр LDTR |

|||||||||

|

|

Таблица GDT |

Таблица LDT |

|

|||||||

|

Базовый адрес |

|

|

|

Базовый адрес |

||||||

|

Базовый адрес |

Базовый адрес |

|||||||||

|

Базовый адрес |

|

Базовый адрес |

||||||||

|

Базовый адрес |

24 |

(32) |

Базовый адрес |

|||||||

|

Базовый адрес |

Базовый адрес |

|||||||||

|

|

16(32) |

|

24(32) |

Физический адрес |

||||||

Старшие 13 бит селектора (индекс) определяют элемент таблицы GDT или LDT в зависимости от бита TI селектора. Извлеченный из таблицы дескрипторов базовый адрес сегмента

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.