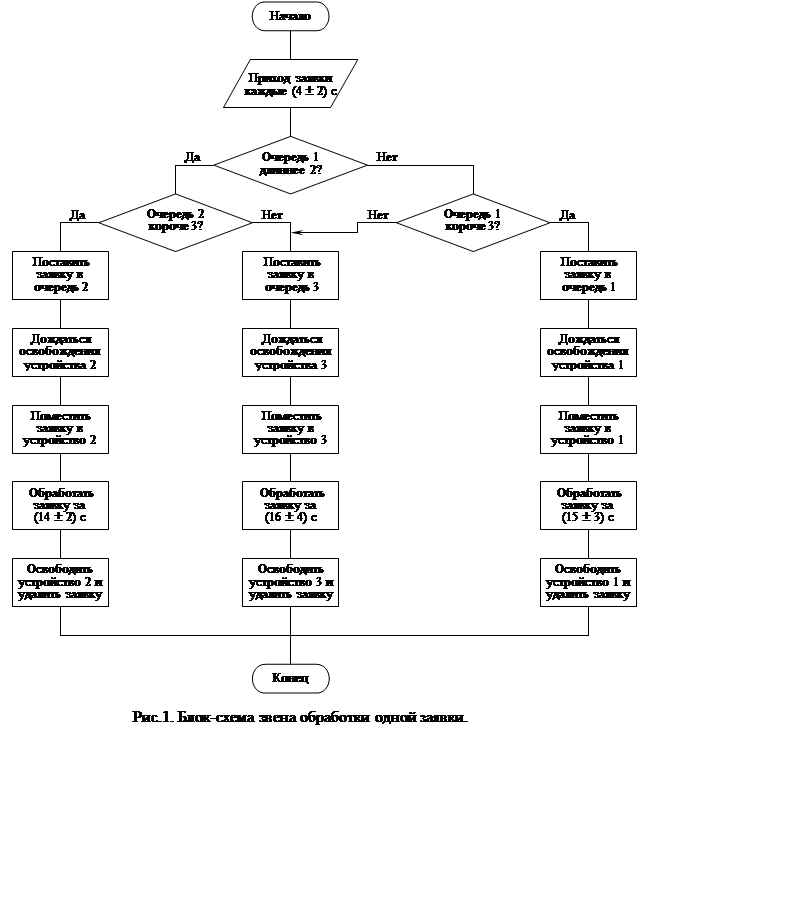

Имеется три независимо работающих процессора с разными временами задержки и устройство неограниченной по размерам внешней памяти. Поток заявок, поступающих с периферийных устройств, обрабатывается на том процессоре, очередь к которому меньше. После обработки заявки происходит захват памяти, куда передаются результаты обработки. Примем в качестве базового варианта следующие значения:

- время обработки заявки в первом устройстве (15 ± 3) с;

- время обработки заявки во втором устройстве (14 ± 2) с;

- время обработки заявки в третьем устройстве (16 ± 4) с;

- время поступления заявок (4 ± 2) с.

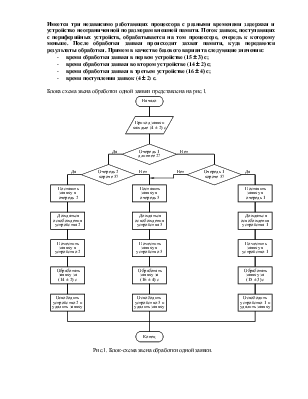

Блока схема звена обработки одной заявки представлена на рис.1.

|

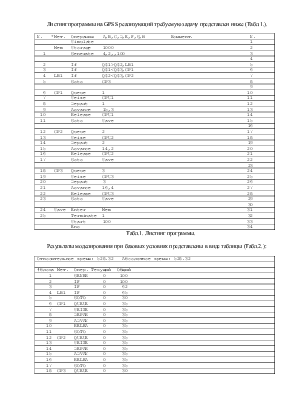

Листинг программы на GPSS реализующий требуемую задачу представлен ниже (Табл.1.).

|

N. *Мет. Операция A,B,C,D,E,F,G,H Коммент. N. |

|

Simulate 1 |

|

Mem Storage 1000 2 |

|

1 Generate 4,2,,100 3 |

|

4 |

|

2 If Q$1>Q$2,LB1 5 |

|

3 If Q$1<Q$3,CP1 6 |

|

4 LB1 If Q$2<Q$3,CP2 7 |

|

5 Goto CP3 8 |

|

9 |

|

6 CP1 Queue 1 10 |

|

7 Seize CPU1 11 |

|

8 Depart 1 12 |

|

9 Advance 15,3 13 |

|

10 Release CPU1 14 |

|

11 Goto Save 15 |

|

16 |

|

12 CP2 Queue 2 17 |

|

13 Seize CPU2 18 |

|

14 Depart 2 19 |

|

15 Advance 14,2 20 |

|

16 Release CPU2 21 |

|

17 Goto Save 22 |

|

23 |

|

18 CP3 Queue 3 24 |

|

19 Seize CPU3 25 |

|

20 Depart 3 26 |

|

21 Advance 16,4 27 |

|

22 Release CPU3 28 |

|

23 Goto Save 29 |

|

30 |

|

24 Save Enter Mem 31 |

|

25 Terminate 1 32 |

|

Start 100 33 |

|

End 34 |

Табл.1. Листинг программы.

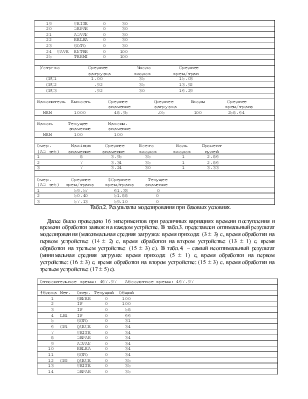

Результаты моделирования при базовых условиях представлены в виде таблицы (Табл.2.):

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.