рис. в.1

рис. 2.1.

Рис. 2.2.

Рис. 2.3.

Рис. 2.4.

Рис. 2.5.

Рис. 2.6.

Рис. 2.7.

Рис.2.8.

Рис. 2.9.

|

Рис. 2.10

Рис. 2.11.

|

Рис. 2.12

![]()

Рис. 2.13. Цепочка обработчиков одного запроса

Рис. 2.14. Перехват прерывания с заменой системной функции собственным обработчиком: а — алгоритм перехвата прерывания, б— алгоритм обработки прерывания

Рис. 2.15. Перехват прерывания путем включения нового обработчика в цепочку системных функций: а — алгоритм перехвата прерывания, б— алгоритм обработки прерывания с передачей управления системному обработчику

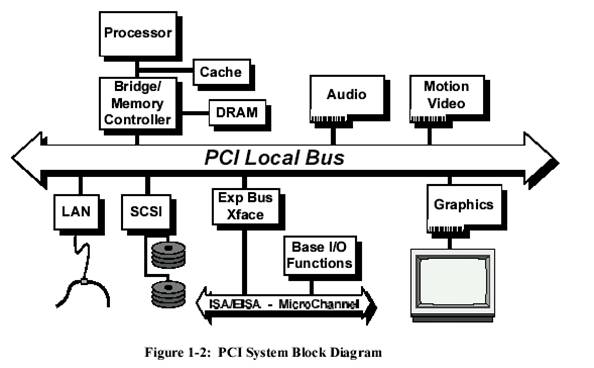

Рис. 2.16. Иллюстрация, показывающая место шины PCI среди других интерфейсов.

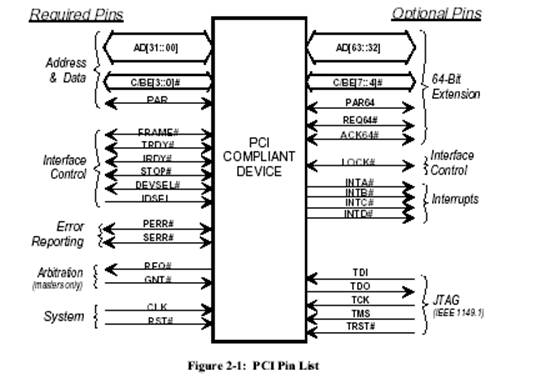

2.17. PCI-устройство

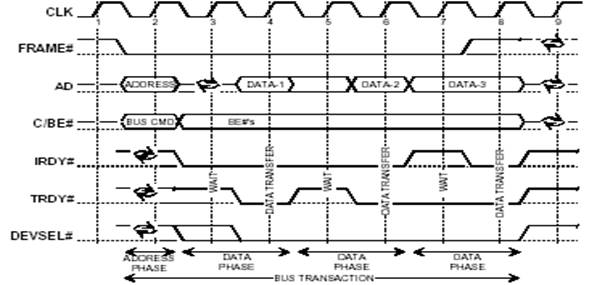

Рис.1.18. Временная диаграмма базовой транзакции чтения

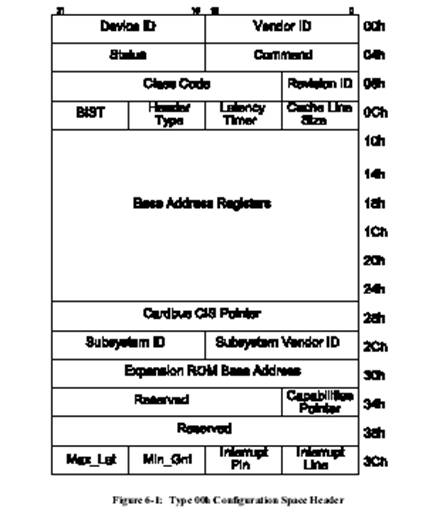

Рис. 2.19. Заголовок пространства конфигурации (Тип 0)

Рис. 3.1. Временная диаграмма передачи байта в стандарте Centronics

Рис. 3.2. Примеры линейных кодов

Рис. 3.3. Временная диаграмма передачи байта 11001010 в формате 8 информационных, контроль на четность, один стоповый по токовой петле

Рис. 3.4. Схема токовой петли для передачи одного сигнла: А — точка подключения источника сигнала, В — точка подключения приемника сигнала

Рис. 3.5. Схема подключения устройств к мультиплексному каналу MIL-1553: ОУ — оконечные устройства, Т — трансформаторы гальванической развязки, Rз — защитные резисторы, Rc — согласующие резисторы.

Рис. 3.6. Структурная схема контроллера Ethernet на трех БИС

Рис. 3.7. Топология шины USB

Рис. 3.8. Логическая взаимосвязь устройств USB

Рис. 3.9. Взаимодействие приложений с устройствами USB

Рис. 3.10. Кодирование данных NRZI

Рис. 3.11. Вставка бита для синхронизации

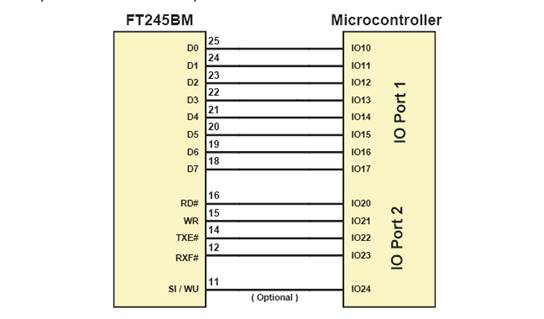

Рис. 3.11. Подключение контроллера FT245BM к портам микроконтроллера

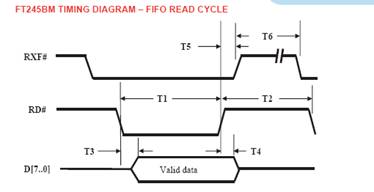

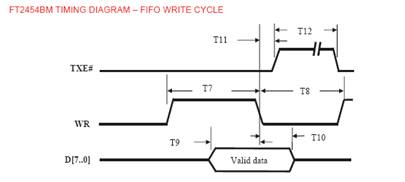

Рис. 3.12. Временные диаграммы чтения/записи данных

Рис. 4.1. Алгоритм кодирования по методу 2,7RLL

Рис. 4.2. Структурная схема накопителя на магнитных дисках

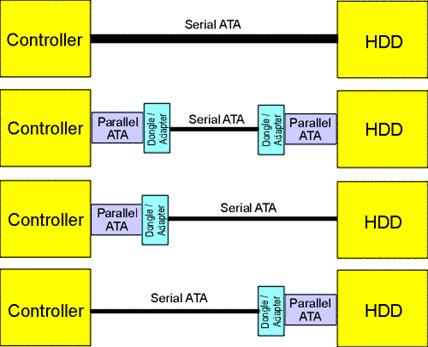

Рис. 4.3. Варианты использования интерфейса SATA

Рис. 4.4. Массив периферийных устройств на шине SSA

Данные на «виртуальном» диске

![]()

RAID-0 (DEC). (Stripping)

RAID-1. «Зеркальные диски» (Mirroring).

RAID-3.

RAID-5.

RAID-6 (возможная реализация)

![]()

Рис. 4.5. Структура микропроцессорной системы управления двухкоординатным приводом.

Рис. 4.6. Линейная интерполяция методом оценочной функции: а) отрезок 0А — желаемая траектория (результат аппроксимации); б) интерполяция раздельными по координатам шагами; в) интерполяция, допускающая одновременные шаги по координатам (X — главная координата).

Рис. 4.7. Алгоритм интерполяции методом оценочной функции: а) алгоритм с раздельными шагами по координатам; б) алгоритм, допускающий одновременные шаги по координатам (Х — главная координата)

Рис.4.8. Структурная схема контроллера SVGA

Рис. 4.9. Последовательный интерфейс видеомонитора

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.