Санкт-Петербургский Государственный Политехнический Университет

Факультет Технической Кибернетики

Кафедра Компьютерных Систем и Программных технологий

ОТЧЕТ

о лабораторной работе №7.

Тема: дешифраторы, мультиплексоры, компараторы.

Выполнил студент гр.3081/1

Преподаватель, __________

Санкт-Петербург

2010г.

1. Цель работы:

Исследование мультиплексоров, дешифраторов, компараторов.

2. Исследование дешифраторов

2.1 Дешифратор на базе LPM_DECODE

Рис. 2.1.1 Схема дешифратора на основе LPM_DECODE.

Промоделируем работу данного дешифратора.

Рис. 2.1.2 Временная диаграмма работы дешифратора.

Дешифраторы предназначены для преобразования кодов. Двоичный дешифратор преобразует двоичный код в унитарный (код «1 из N»). Если на входы поступает код, соответствующий числу k в двоичной записи, то "1" ("0") появляется на выходе с номером k, считая от 0. Дешифратор, имеющий n входов, имеет N = 2n выходов, что соответствует числу различных комбинаций в n-разрядном двоичном коде.

В данном случае, дешифратор имеет 3 входа, следовательно на выходе имеем 8 разрядный код. На временной диаграмме видно, что при подаче, например на вход значения 1, то выход q1 примет значения 1, а все остальные примут значения 0.

Асинхронная установка CLR в ноль позволяет в любой моменты времени сбросить в 0 все выходы. Что продемонстрировано на Рис. 2.1.2 Дешифратор работает только при сигнале разрешения enable=1, и clkENA соответственно.

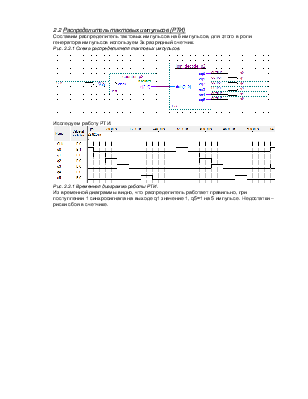

2.2 Распределитель тактовых импульсов (РТИ)

Составим распределитель тактовых импульсов на 6 импульсов, для этого в роли генератора импульсов используем 3х разрядный счетчик.

Рис. 2.2.1 Схема распределителя тактовых импульсов.

Исследуем работу РТИ.

Рис. 2.2.1 Временная диаграмма работы РТИ.

Из временной диаграммы видно, что распределитель работает правильно, при поступлении 1 синхросигнала на выходе q1 значение 1, q5=1 на 5 импульсе. Недостатки – риски сбоя в счетчике.

3. Исследование мультиплексоров

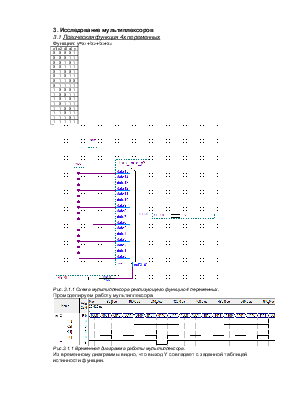

3.1 Логическая функция 4х переменных

Функция: y=x1+!x2+!x3+x4

|

х1 х2 х3 х4 y |

|

0 0 0 0 1 |

|

0 0 0 1 1 |

|

0 0 1 0 1 |

|

0 0 1 1 1 |

|

0 1 0 0 1 |

|

0 1 0 1 1 |

|

0 1 1 0 0 |

|

0 1 1 1 1 |

|

1 0 0 0 1 |

|

1 0 0 1 1 |

|

1 0 1 0 1 |

|

1 0 1 1 1 |

|

1 1 0 0 1 |

|

1 1 0 1 1 |

|

1 1 1 0 1 |

|

1 1 1 1 1 |

Рис. 3.1.1 Схема мультиплексора реализующего функцию 4 переменных.

Промоделируем работу мультиплексора.

Рис.3.1.1 Временная диаграмма работы мультиплексора.

Из временному диаграммы видно, что выход Y совпадает с заданной таблицей истинности функции.

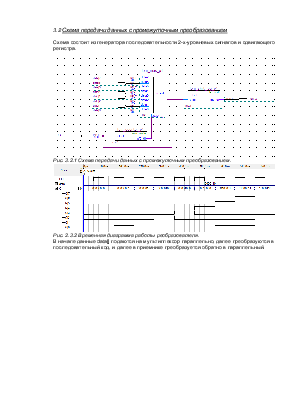

3.2 Схема передачи данных с промежуточным преобразованием

Схема состоит из генератора последовательности 2-х-уровневых сигналов и сдвигающего регистра.

Рис. 3.2.1 Схема передачи данных с промежуточным преобразованием.

Рис. 2.3.2 Временная диаграмма работы реобразователя.

В начале данные data[] подаются на мультиплексор параллельно, далее преобразуются в последовательный код, и далее в приемнике преобразуется обратно в параллельный.

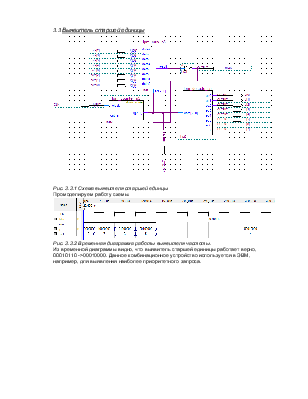

3.3 Выявитель старшей единицы

Рис. 3.3.1 Схема выявителя старшей единцы.

Рис. 3.3.1 Схема выявителя старшей единцы.

Промоделируем работу схемы.

Рис. 3.3.2 Временная диаграмма работы выявителя частоты.

Из временной диаграммы видно, что выявитель старшей единицы работает верно,

00010110 ->00010000. Данное комбинационное устройство используется в ЭВМ, например, для выявления наиболее приоритетного запроса.

4. Исследование компараторов

4.1Компаратор сравнения 32-разрядных чисел

Рис. 4.1.1 Схема компаратора сравнивающего 32-разрядные числа.

Промоделируем работу компаратора, для этого подадим разные числа на входы DATA_A[] и DATA_B[].

Рис. 4.1.2 Временная диаграмма работы компаратора.

Как видно из временной диаграммы, компаратор работает верно, на 5,7 и 8 импульсах на выходе Q мы наблюдаем 0 так как эти разряды отличаются, в остальных случаях, когда одноразрядные фрагменты совпадают, мы видим на Q 1.

4.2 Исследование счетчика-делителя управляемого кодом

Рис.4.2.1 Схема счетчика-делителя.

Рис.4.2.1 Схема счетчика-делителя.

Моделирование работы счетчика-делителя.

Рис.4.2.2 Временная диаграмма работы счетчика делителя.

Как видно из временной диаграммы, схема работает верно, при достижении соответствия между значением счетчика и числом поданным на вход DATA_B[] то происходит сброс счетчика по фронту импульса (синхронный сброс).

5. Выводы

В ходе работы были исследованы устройства сравнения, дешифраторы и мультиплексоры.

Дешифраторы предназначены для преобразования кодов, нами был исследован дешифратор на 3 входа и 8 выходов. Рис. 2.1.1

Так же был разработан распределитель тактовых импульсов на 6 каналов. Рис.2.2.1

На основе LPM_MUX была реализована функция 4х переменных (y=x1+!x2+!x3+x4).

Так же, была разработана схема выявителя старшей единицы, такие устройства позволяют, например, выявлять наиболее приоритетные запросы.

Так же был разработан компаратор, осуществляющий сравнение 2х 32х разрядных чисел.

Последним был разработан счетчик-делитель, который синхронно сбрасывает счетчик в случае равенства загруженных данных через DATA_B[] и значения в счетчике. Рис. 4.2.1

Все исследованные устройства работают верно.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.