Санкт-Петербургский Государственный Политехнический Университет

Факультет Технической Кибернетики

Кафедра Автоматики и Вычислительной техники

Отчет

по лабораторной работе №2

Триггеры.

(тема работы)

Схемотехника

(наименование дисциплины)

Работу выполнила студентка 3081/1

Преподаватель И.

Санкт – Петербург

2009

1. Цель работы

-Закрепление знания характеристик и режимов работы триггеров основных типов;

- получение практических навыков тестирования и управления триггерами;

- получение навыков ввода проекта в графическом редакторе пакета Quartus II, тестирования и отладки проекта и анализа временных характеристик триггеров;

- получение навыков отладки цифровых устройств данного класса на физической модели: конфигурирование СБИС ПЛ и экспериментальная проверка работы типовых устройств с триггерами при использовании лабораторной платы DiLab.

2. Асинхронный RS – триггер

|

Дискретное время |

Входные переменные |

Состояния |

Режим работы |

||

|

t |

S(t) |

R(t) |

Q(t) |

nQ(t) |

|

|

0 |

0 |

1 |

1 |

0 |

Установка 1 |

|

|

1 |

1 |

1 |

0 |

Хранение 1 |

|

|

1 |

0 |

0 |

1 |

Установка 0 |

|

|

1 |

1 |

0 |

1 |

Хранение 0 |

|

|

0 |

1 |

1 |

0 |

Установка 1 |

|

|

0 |

0 |

1 |

1 |

Особое состояние |

|

|

1 |

0 |

0 |

1 |

Установка 0 |

|

|

0 |

0 |

1 |

1 |

Особое состояние |

|

|

0 |

1 |

1 |

0 |

Установка 1 |

Табл. 2.1. Таблица переходов асинхронного RS-триггера.

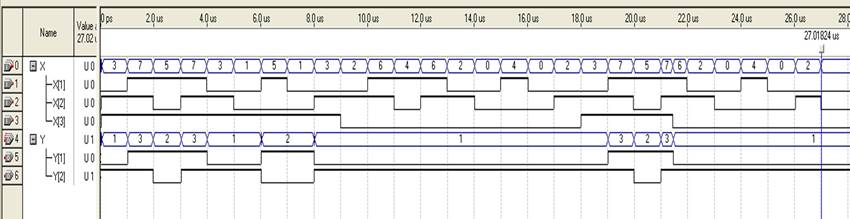

Рис 2.1. Схема асинхронного RS – триггера

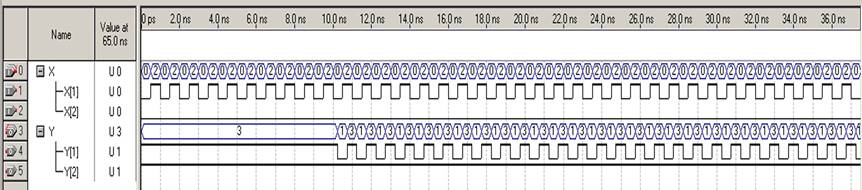

Рис 2.2. Временное моделирование устройства

Рис 2.2. Временное моделирование устройства

Рис 2.3. Переход модели триггера в режим генерации

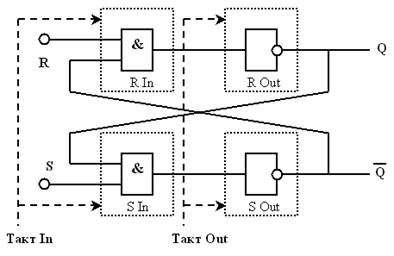

3. RS-триггер, синхронизируемый уровнем

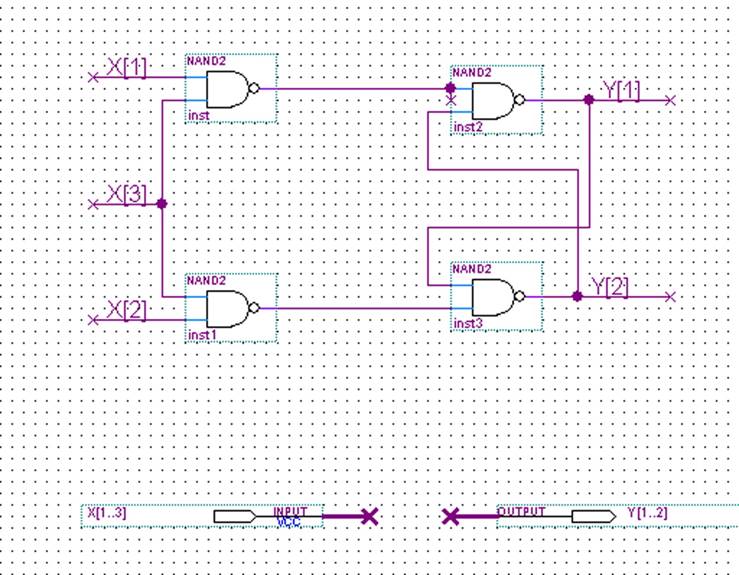

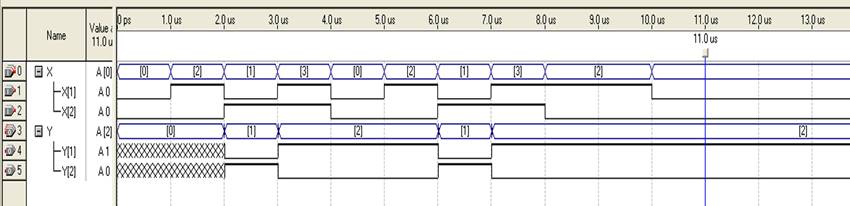

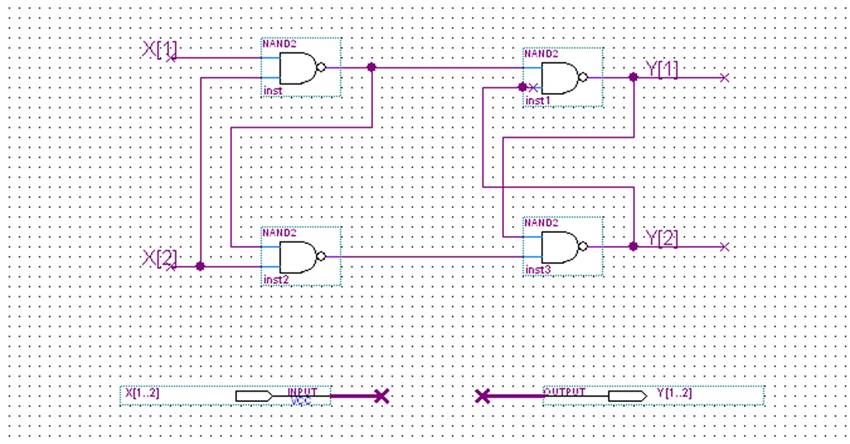

Рис 3.1. Схема

Рис 3.2. Временное моделирование устройства

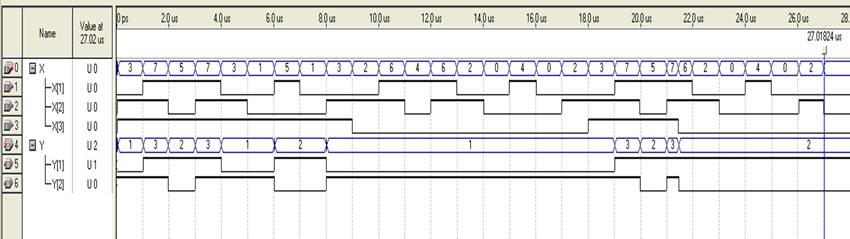

Рис 3.2. Временное моделирование устройства

Рис 3.2. RS-триггер, синхронизируемый уровнем

с учетом задержки

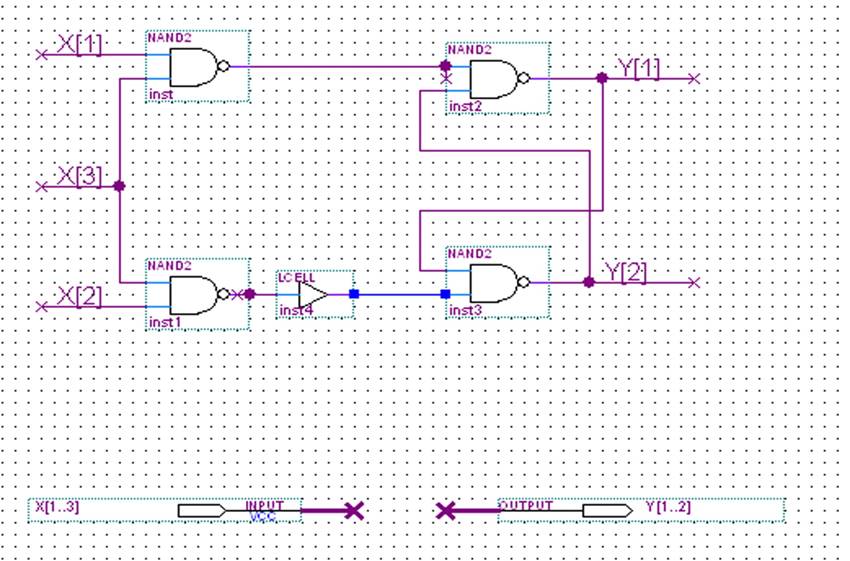

Рис 3.2. RS-триггер, синхронизируемый уровнем

с учетом задержки

Рис 3.3. Временное моделирование устройства

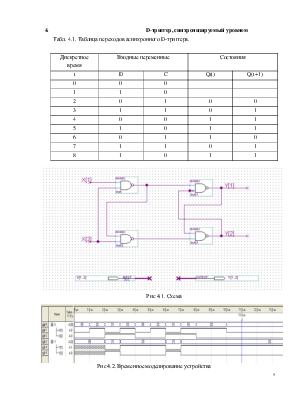

4. D-триггер, синхронизируемый уровнем

Табл. 4.1. Таблица переходов асинхронного D-триггера.

|

Дискретное время |

Входные переменные |

Состояния |

||

|

t |

D |

C |

Q(t) |

Q(t+1) |

|

0 |

0 |

0 |

||

|

1 |

1 |

0 |

||

|

2 |

0 |

1 |

0 |

0 |

|

3 |

1 |

1 |

0 |

1 |

|

4 |

0 |

0 |

1 |

1 |

|

5 |

1 |

0 |

1 |

1 |

|

6 |

0 |

1 |

1 |

0 |

|

7 |

1 |

1 |

0 |

1 |

|

8 |

1 |

0 |

1 |

1 |

Рис 4.1. Схема

Рис 4.1. Схема

Рис 4.2. Временное моделирование устройства

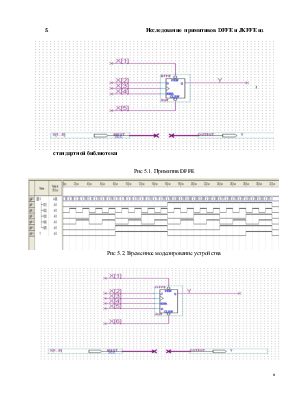

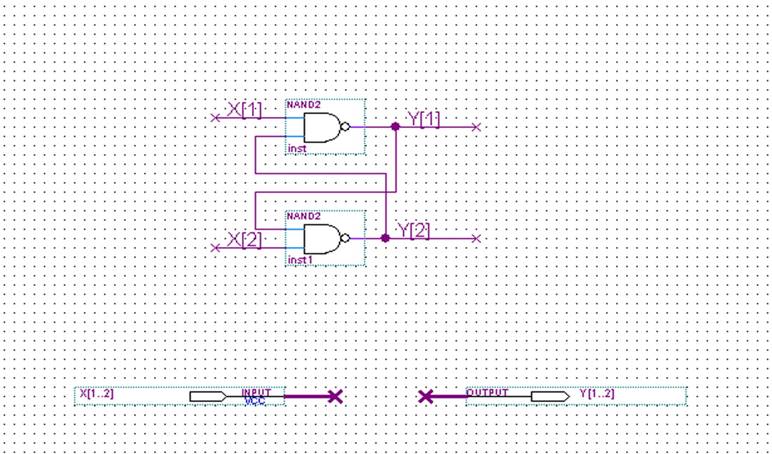

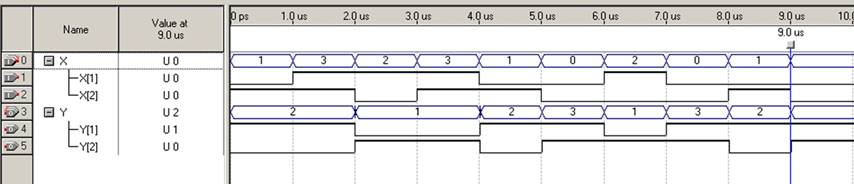

5.

Исследование примитивов DFFE и JKFFE из стандартной

библиотеки

Исследование примитивов DFFE и JKFFE из стандартной

библиотеки

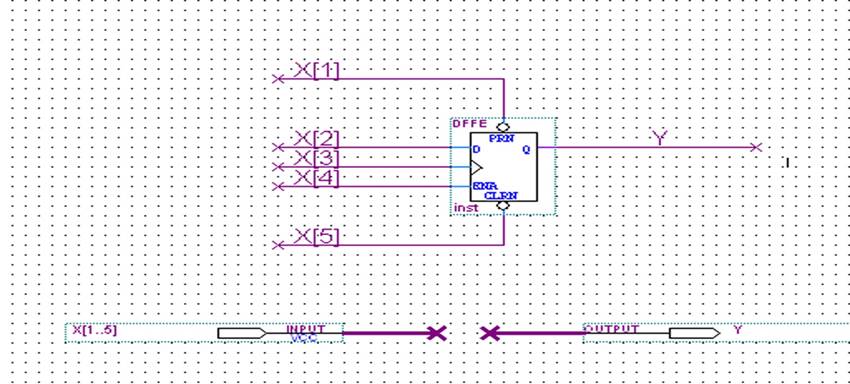

Рис 5.1. Примитив DFFE

Рис 5.1. Примитив DFFE

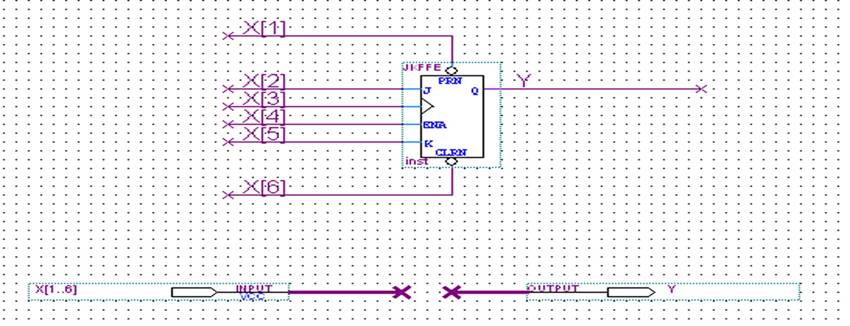

Рис 5.2. Временное моделирование устройства

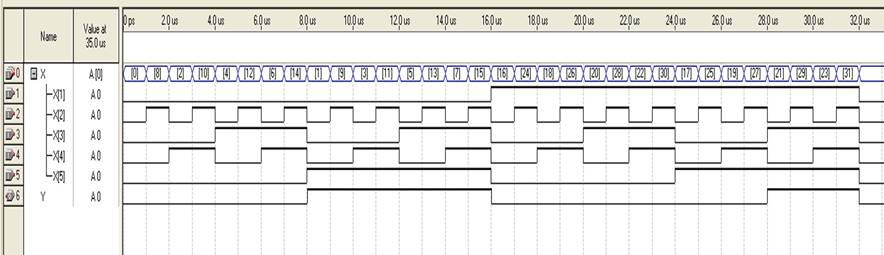

Рис 5.3. Примитив JKFFE

Рис 5.4. Временное моделирование устройства

6.

DFF триггер без асинхронных установок

DFF триггер без асинхронных установок

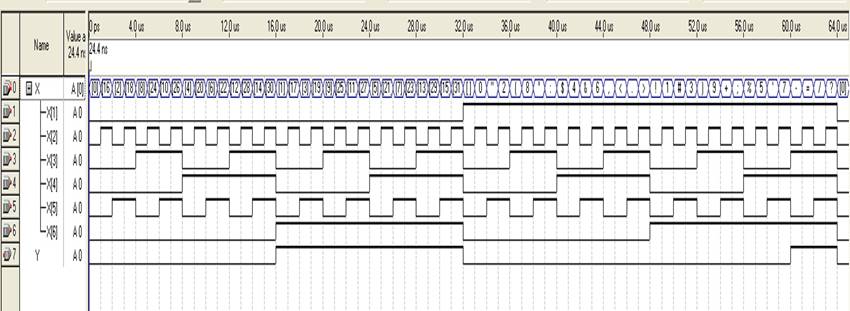

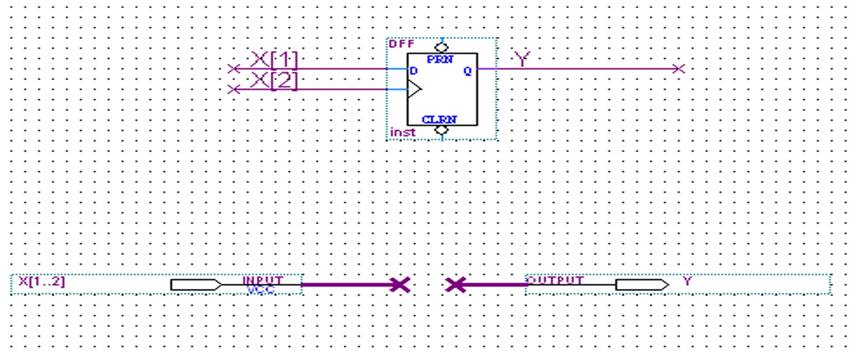

Рис 6.1. Схема

Рис 6.1. Схема

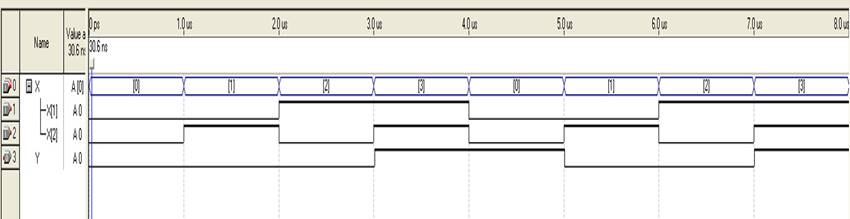

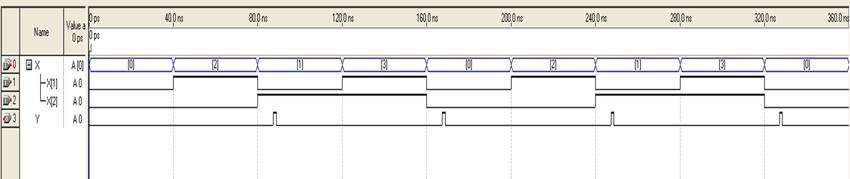

Рис 6.2. Временное моделирование устройства

7.

Генератор коротких импульсов

Генератор коротких импульсов

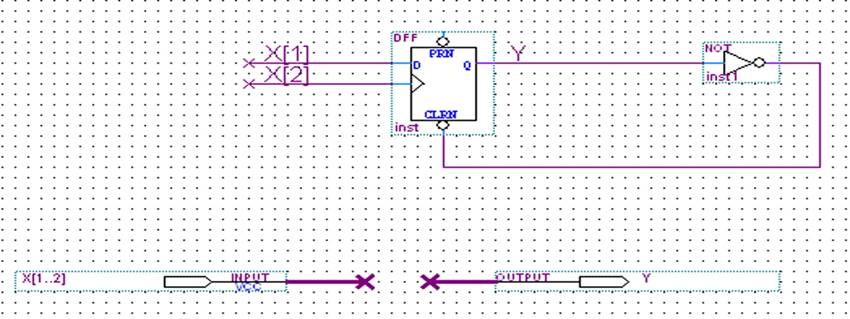

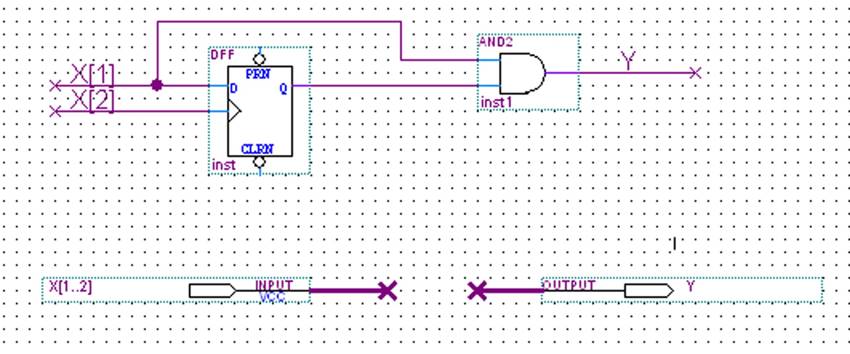

Рис 7.1. Схема

Рис 7.2. Временное моделирование устройства

Рис 7.2. Временное моделирование устройства

8.  Устройство удвоения частоты

Устройство удвоения частоты

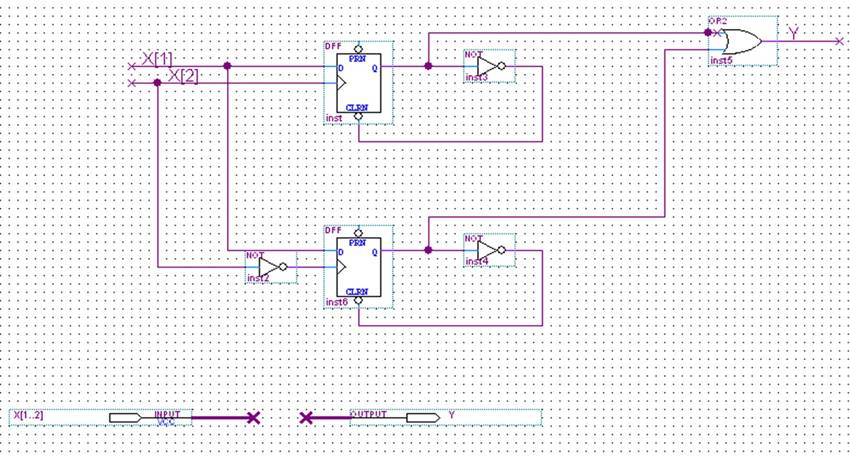

Рис 8.1. Схема

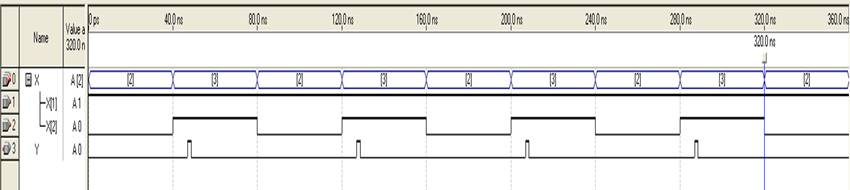

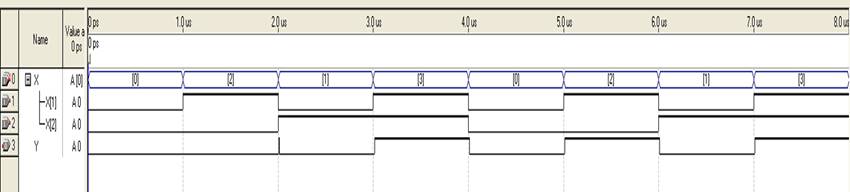

Рис 8.2. Временное моделирование устройства

Рис 8.2. Временное моделирование устройства

9. Устройство выявления фронта

Рис 9.1. Схема

Рис 9.1. Схема

Рис 9.2. Временное моделирование устройства

10. Выводы

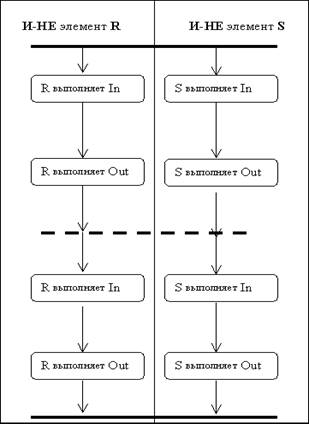

Основой всех триггерных устройств является асинхронный RS-триггер (элементарная ячейка памяти), который был реализован на двух ЛЭ 2И-НЕ, охваченных перекрестной положительной обратной связью. Временное моделирование устройства показало, что при подаче комбинации S=0, R=0 блокируются связи между ЛЭ, на выходах Q и nQ устанавливаются 1, и устройство утрачивает свойства триггера (запрещенная комбинация). Установка триггера в 1 или 0 осуществляется независимо от предыдущего состояния подачей сигнала низкого уровня на входы соответственно S или R (пп. 1, 2).

В режиме

генерации компоненты триггера синхронно меняют свое состояние с 11 на 00 и

обратно.

В режиме

генерации компоненты триггера синхронно меняют свое состояние с 11 на 00 и

обратно.

На диаграмме элементарные действия элементов показаны на одних горизонтальных линиях, хотя в реальности они могут быть разнесены во времени, более того на одно действие какого-либо элемента может приходиться любое количество действий другого. Если оба элемента совершенно одинаковые, начинают работать одновременно и у них одна и та же скорость работы, период запуска соответствующей задачи, то некоторое время триггер будет генерировать. Причем чем меньше период запуска, тем вероятнее срыв генерации. Итак, для генерации RS-триггера в параллельной среде необходимы искусственные условия, крайне редкие в реальной жизни (п. 3).

Для приема информации в фиксированные интервалы времени используются синхронные триггеры. Простейший из них – RS-триггер , синхронизируемый уровнем. Установка этого триггера по входам S и R осуществляется высоким уровнем и возможна при разрешающем состоянии C=1. При C=0 состояние триггера не меняется при любых комбинациях S и R , т.е. триггер синхронизируется уровнем, а не перепадом . При переходе триггера из особого состояния в состояние хранения (спад на входе С при R=S=1), модель переходит в устойчивое состояние Y[2] = 0. Вследствие добавления задержки между логическими элементами первого и второго ряда устойчивое состояние меняется на противоположное (S out = 1 – не успевает переключиться, R out = 0; Y[2] = 1) (п. 4).

В RS-триггере производится парафазная запись (необходимо подавать сигналы на входы S и R). Осуществить переход к однофазной записи (уменьшить число подводящих проводов) позволяет использование D-триггера. Установка триггера осуществляется при C=1. При C=0 любое изменение состояния D не влияет на состояние триггера (синхронизация уровнем) (п. 5).

Синхронизируемые уровнем RS- и D-триггеры в течение интервала времени, когда C=1, "прозрачны" для входных сигналов и ведут себя в течение этого времени как асинхронные триггеры, когда изменения сигналов на входах вызывают сразу же соответствующие изменения состояний выхода. Эта особенность ограничивает область применения триггеров, синхронизируемых уровнем. Большинство триггеров, являются синхронными триггерами, синхронизируемыми положительным перепадом (фронтом) (примитивы DFFE и JKFFE). Исходя из анализа их работы следует, что для обеспечения приоритетности установки в ноль, в схему рис. 3.1. следует добавить входы асинхронной установки PRN и асинхронного сброса CLRN (п. 6).

На основе триггеров синтезируются такие устройства как генератор коротких импульсов (примитив DFF) (п. 8), устройство удвоения частоты (п. 9), устройство выявления фронта (п. 10). В первом случае увеличить длительность формируемого импульса можно, добавив элемент задержки в цепь обратной связи. Чтобы создать устройство выявления спада, надо во входной цепи

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.