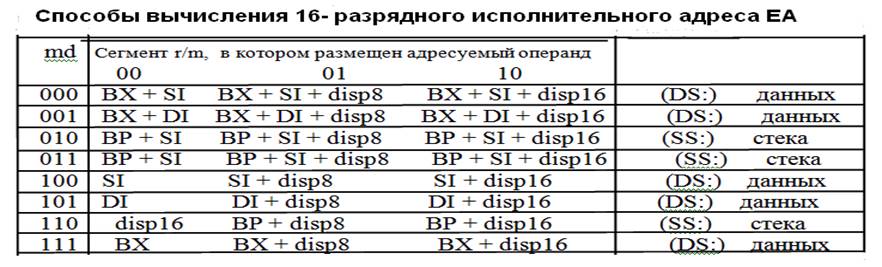

В качестве базового и индексного регистров при 32-битной адресации можно использовать любой из 32-разрядных регистров общего назначения, а при 16-битной адресации - только регистры BP, BX и SI, DI соответственно. Базовый и индексный регистры удобно применять для формирования адресов, изменяемых в процессе выполнения программы, например, для указания начала одной записи в массиве записей или для определения начала одномерного массива в многомерном.

Режимы адресации с помощью постбайта:

Формирование адресации:

1. Прямая - при работе с простыми переменными и константами, местоположение которых в памяти не меняется в процессе выполнения задачи. Исполнительный адрес операнда ЕА содержится непосредственно в коде команды и обычно следует за постбайтом адресации.

2. Абсолютная - применяется только в командах безусловных переходов и вызова подпрограмм. В результате выполнения команды смещение передается в указатель команд ЕIP, а селектор сегмента - в регистр CS. Постбайт адресации также не требуется.

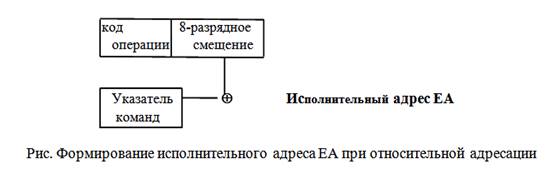

3. Относительная - используют в командах условных переходов и в командах безусловной передачи управления при реализации коротких внутрисегментных перeходов.

4. Байт SIB - в командах с 32-битовой адресацией при значении поля r/m=100В и значении mod # 11 в коде команды присутствует дополнительный байт адресации SIB (Scale - Index - Base), который за счет дополнительного кодирования компонент адресации расширяет возможности процессора при вычислении исполнительного адреса ЕА.

Двухбитное поле Scaleкодирует

значение масштабного множителя (1,2,4 или 8), указывающего размер элементов массива

при использовании индексной адресации. Трехбитовые поля Index и Baseопределяют имена

регистров общего назначения, используемых как индексный или базовые

регистры. При наличии байта SIB 32-разрядное внутрисегментное смещение

(исполнительный адрес EA) вычисляется по формулой:

Двухбитное поле Scaleкодирует

значение масштабного множителя (1,2,4 или 8), указывающего размер элементов массива

при использовании индексной адресации. Трехбитовые поля Index и Baseопределяют имена

регистров общего назначения, используемых как индексный или базовые

регистры. При наличии байта SIB 32-разрядное внутрисегментное смещение

(исполнительный адрес EA) вычисляется по формулой:

EA = Base + Index*Scale + Disp,

где Base, Index, Scale (масштаб), Disp (смещение) – компоненты ЕА.

Для

вычисления EA могут быть использованы любые или все переменные: база,

индекс и смещение. Переменные база и индекс являются величинами,

хранящимися в общих регистрах, а величина смещения содержится в коде

команды.

Для

вычисления EA могут быть использованы любые или все переменные: база,

индекс и смещение. Переменные база и индекс являются величинами,

хранящимися в общих регистрах, а величина смещения содержится в коде

команды.

18. Организация виртуальной памяти процессора PentiumIV.

При виртуальной адресации часть используемого адресного пространства располагается в основной памяти, а другая его часть - на дисковой памяти. При отсутствии требуемой информации (команд или данных) в основной памяти автоматически под управлением операционной системы осуществляется пересылка требуемых частей программы из дискового накопителя в основную память (отметим, что дисковая память примерно в 400 раз дешевле чем основная оперативная память). Для реализации виртуальной памяти, кроме аппаратных средств процессора, необходимы также мощные программные средства.

В процессоре Р4 используют две основные модели физической памяти: сегментированную память и память со страничной организацией.

• При сегментировании памяти сегмент является единицей логического адресного пространства, которая предоставляется процессору для выполнения задачи, при этом логическое адресное пространство задачи может состоять из одного или нескольких сегментов. На расположение сегментов не накладывается никаких специальных ограничений. Сегменты могут быть смежными, раздельными, перекрываться частично или полностью. Сегменты используются для объединения областей памяти, имеющих общие атрибуты, например, сегменты кода, данных или стека.

• Внутри сегмента применяется линейная адресация относительно начала сегмента, и физический адрес, по существу, скрыт от программиста.

• Логический адрес сегментированного адресного пространства определяется двумя составляющими: базовым адресом сегмента (обычно задается программой операционной системы) и внутрисегментным смещением (вычисляется операционным блоком процессора).

• Механизм страничного преобразования выполняет распределение памяти блоками фиксированного размера (страницами) с автоматическим наложением блоков на адреса физической памяти.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.