процессе работы программы осуществляется бесконечный цикл переходов по адресам 0000 -> 0001 -> 0010 -> 0011 -> 1010 -> 0010 -> 0011 -> …

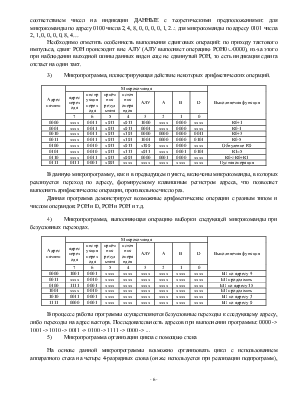

6) Микропрограмма, демонстрирующая обращение к подпрограмме и возврат из нее.

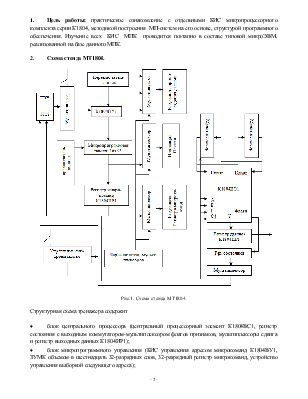

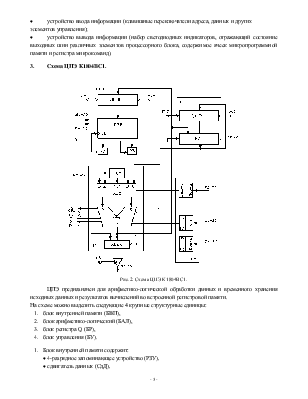

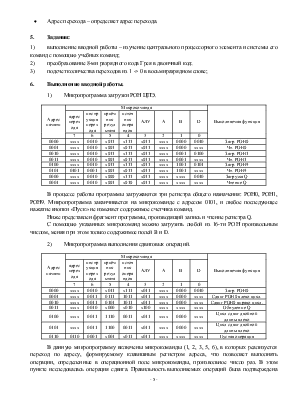

Микропрограмма, являющаяся реализацией диаграммы переходов на Рис.3.

Программа Подпрограмма

Рис.3.

|

Адрес памяти |

Микрокоманда |

Выполняемая функция |

|||||||

|

адрес перехода |

инструкция перехода |

приёмник результата |

источник операндов |

АЛУ |

А |

В |

D |

||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

||

|

0000 |

хххх |

0010 |

хххх |

хххх |

хххх |

хххх |

хххх |

хххх |

Продолжить |

|

0001 |

1000 |

0101 |

хххх |

хххх |

хххх |

хххх |

хххх |

хххх |

Переход к подпрограмме |

|

0010 |

хххх |

0010 |

хххх |

хххх |

хххх |

хххх |

хххх |

хххх |

Продолжить |

|

0011 |

0000 |

0001 |

хххх |

хххх |

хххх |

хххх |

хххх |

хххх |

БП к адресу 0000 |

|

1000 |

хххх |

0010 |

хххх |

хххх |

хххх |

хххх |

хххх |

хххх |

Продолжить |

|

1001 |

хххх |

0010 |

хххх |

хххх |

хххх |

хххх |

хххх |

хххх |

Продолжить |

|

1010 |

хххх |

0110 |

хххх |

хххх |

хххх |

хххх |

хххх |

хххх |

Возврат из подпрограммы |

7) Микропрограмма, организации вложения подпрограмм.

Данная микропрограмма реализована с помощью аппаратного стека (на четыре 4-разрядных слова), поэтому возможно четыре вложения подпрограмм.

|

Адрес памяти |

Микрокоманда |

Выполняемая функция |

|||||||

|

адрес перехода |

инструкция перехода |

приёмник результата |

источник операндов |

АЛУ |

А |

В |

D |

||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

||

|

0000 |

хххх |

0010 |

хххх |

хххх |

хххх |

хххх |

хххх |

хххх |

Продолжить |

|

0001 |

0011 |

0101 |

хххх |

хххх |

хххх |

хххх |

хххх |

хххх |

Переход к подпрограмме 1 |

|

0010 |

0000 |

0001 |

хххх |

хххх |

хххх |

хххх |

хххх |

хххх |

БП к адресу 0000 |

|

0011 |

0110 |

0101 |

хххх |

хххх |

хххх |

хххх |

хххх |

хххх |

Переход к подпрограмме 2 |

|

0100 |

0111 |

0101 |

хххх |

хххх |

хххх |

хххх |

хххх |

хххх |

Переход к подпрограмме 3 |

|

0101 |

хххх |

0110 |

хххх |

хххх |

хххх |

хххх |

хххх |

хххх |

Возврат из подпрограммы 1 |

|

0110 |

хххх |

0110 |

хххх |

хххх |

хххх |

хххх |

хххх |

хххх |

Возврат из подпрограммы 2 |

|

0111 |

0110 |

0101 |

хххх |

хххх |

хххх |

хххх |

хххх |

хххх |

Переход к подпрограмме 2 |

|

1000 |

1010 |

0101 |

хххх |

хххх |

хххх |

хххх |

хххх |

хххх |

Переход к подпрограмме 4 |

|

1001 |

хххх |

0110 |

хххх |

хххх |

хххх |

хххх |

хххх |

хххх |

Возврат из подпрограммы 3 |

|

1010 |

0110 |

0101 |

хххх |

хххх |

хххх |

хххх |

хххх |

хххх |

Переход к подпрограмме 2 |

|

1011 |

1101 |

0101 |

хххх |

хххх |

хххх |

хххх |

хххх |

хххх |

Переход к подпрограмме 5 |

|

1100 |

хххх |

0110 |

хххх |

хххх |

хххх |

хххх |

хххх |

хххх |

Возврат из подпрограммы 4 |

|

1101 |

хххх |

0010 |

хххх |

хххх |

хххх |

хххх |

хххх |

хххх |

Продолжить |

|

1110 |

хххх |

0110 |

хххх |

хххх |

хххх |

хххх |

хххх |

хххх |

Возврат из подпрограммы 5 |

Последовательность адресов выполняемых микрокоманд:

0000 ® 0001 ® нач 1{0011 ® нач 2( 0110 )конец 2 ® 0100 ® нач 3[ 0111 ® нач 2( 0110 )конец 2 ® 1000 ® нач 4 ( 1010 ® нач 2( 0110 )конец 2 ® 1011 ® нач 5( 1101 ® 1110 ) конец 5 ® 1100 ) конец 4 ® 1001 ] конец 3 ® 0101 } конец 1 ® 0010 ® 0000 ® 0001 …

Скобки показывают вложенность подпрограмм, а цифра на верху показывает номер вложения.

8) Микропрограмма, организации условных переходов.

При запуске будут отображаться адреса: 0, 1, 2 (15 раз), 0, 1, 15 и т.д.

|

Адрес памяти |

Микрокоманда |

Выполняемая функция |

|||||||

|

адрес перехода |

инструкция перехода |

приёмник результата |

источник операндов |

АЛУ |

А |

В |

D |

||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

||

|

0000 |

хххх |

0010 |

х011 |

х011 |

1000 |

хххх |

0000 |

хххх |

R0+1, продолжить |

|

0001 |

1111 |

1111 |

х001 |

хххх |

хххх |

хххх |

хххх |

хххх |

УП по С4 |

|

0010 |

0000 |

0001 |

х001 |

хххх |

хххх |

хххх |

хххх |

хххх |

БП к 0 |

|

1111 |

хххх |

0010 |

х001 |

хххх |

хххх |

хххх |

хххх |

хххх |

Продолжить |

Условные переходы в микропроцессоре К1804 реализуются по содержимому регистра состояния. В данной микропрограмме реализован УП по значению флага переноса. Следует отметить, что результаты в регистр состояния записываются после выполнения операции в момент прихода тактового импульса, поэтому условный переход по этим результатам может быть сделан лишь в следующей команде. Все это приводит кто тому, что программист обязан после некоторой команды, по результату которой выполняется УП, вставлять отдельную команду реализации УП. При наличии ограниченной памяти сложнее написать длинные микропрограммы.

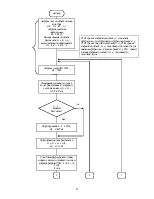

7. Преобразование 8-ми разрядного кода Грея в двоичный код.

Исходное число в коде Грея: g7, g6, g5, g4, g3, g2, g1, g0.

Число, преобразованное в 2-й код: b7, b6, b5, b4, b3, b2, b1, b0.

Преобразование осуществляется

следующим образом: ![]() ,

, ![]() ,

, ![]() .

.

В данной программе

перекодировка из кода Грея в двоичный код осуществляется путем рассмотрения

чисел по полубайтам. После выполнения по определенным правилам перекодировки

старшего полубайта, происходит перекодировка младшего. Основная трудность в

реализации данного алгоритма заключается в необходимости учитывать значения

бита b4 при переходе к анализу старшего бита младшего

полубайта b3: ![]() .

.

В рассматриваемом алгоритме маска (М) осуществляет выявление для каждого bi-го бита единицы в gi-ом бите. Вспомогательная переменная S представляет собой сумму по модулю 2 gi: со старшего бита до gi+1. На основе этой переменной записывается очередной разряд двоичного числа. На каждом шаге маска сдвигается в сторону младших разрядов, пока не обнулится, это и является признаком того, что анализ полубайта закончен.

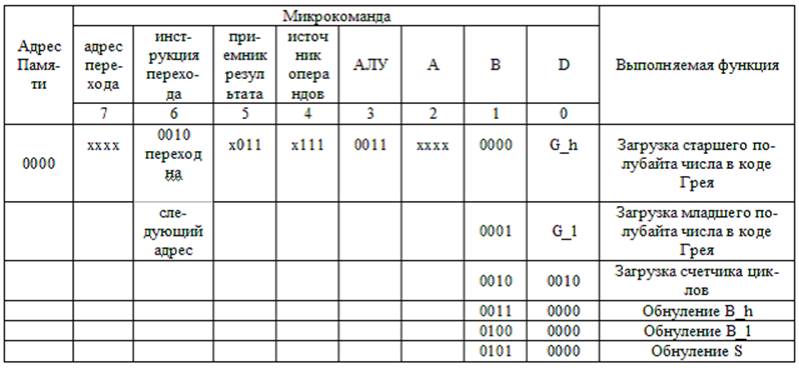

Начальная загрузка:

Текст программы:

|

Адрес памяти |

Микрокоманда |

Выполняемая функция |

|||||||

|

адрес перехода |

инструкция перехода |

приемник результата |

источник операндов |

АЛУ |

А |

В |

D |

||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

||

|

0000 |

хххх |

0010 |

х011 |

х111 |

x011 |

хххх |

0110 |

1000 |

Загрузка маски М |

|

0001 |

хххх |

0010 |

х001 |

х001 |

x100 |

0000 |

0110 |

хххх |

G_h^M |

|

0010 |

0100 |

1100 |

х001 |

х011 |

x011 |

хххх |

хххх |

хххх |

УП Z=1? |

|

0011 |

хххх |

0010 |

х011 |

х001 |

x110 |

0110 |

0101 |

хххх |

S=S |

|

0100 |

хххх |

0010 |

х011 |

х001 |

x011 |

0101 |

0011 |

хххх |

B_h=B_h |

|

0101 |

хххх |

0010 |

0101 |

0011 |

x011 |

хххх |

0101 |

хххх |

0->S |

|

0110 |

хххх |

0010 |

0101 |

0011 |

x011 |

хххх |

0110 |

хххх |

0->M |

|

0111 |

0001 |

0100 |

х001 |

х001 |

x011 |

хххх |

хххх |

хххх |

УП Z=0? |

|

1000 |

хххх |

0010 |

х011 |

х011 |

0001 |

хххх |

0010 |

хххх |

count = count - 1 |

|

1001 |

1110 |

1100 |

х001 |

х011 |

x011 |

хххх |

хххх |

хххх |

УП Z=1? |

|

1010 |

хххх |

0010 |

0101 |

1101 |

x100 |

0101 |

0101 |

0001 |

S=B_h^0001- выявление единицы в бите b4, циклический сдвиг вправо |

|

1011 |

хххх |

0010 |

х011 |

х100 |

0011 |

0011 |

0100 |

хххх |

Сохранение полученного B_h в R4: R4:=R3 |

|

1100 |

хххх |

0010 |

х011 |

х100 |

x011 |

0001 |

0000 |

хххх |

Запись на место R_h R_l для продолжения перекодировки: R0:=R1 |

|

1101 |

0000 |

0001 |

х011 |

х111 |

x011 |

хххх |

0011 |

0000 |

Обнуление B_h для перекодировки младшего полубайта, переход на адрес из Рг микрокоманд |

|

1110 |

xxxx |

0010 |

х001 |

х011 |

x011 |

xxxx |

0011 |

xxxx |

Вывод на Шд B_l |

|

1111 |

1110 |

0001 |

х001 |

х011 |

x011 |

xxxx |

0100 |

xxxx |

Вывод на Шд B_h |

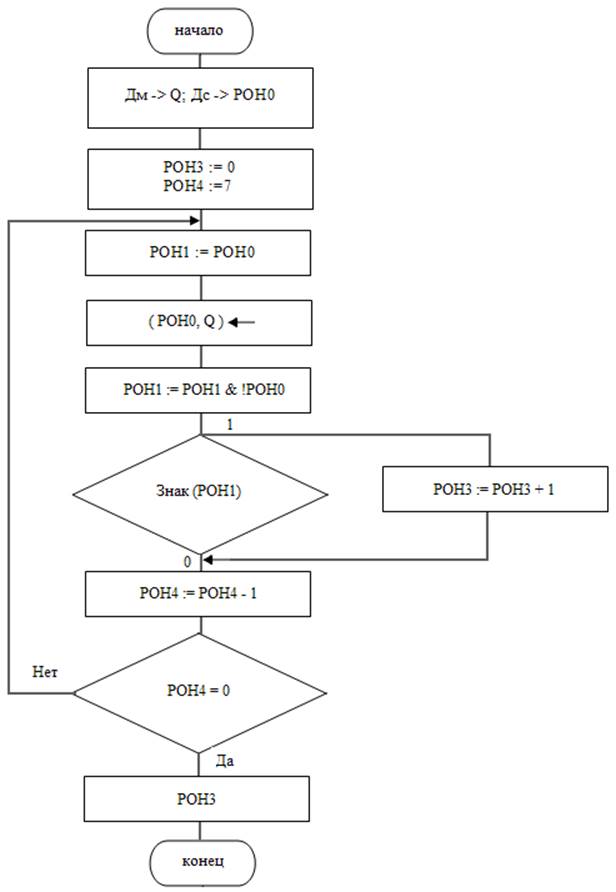

8. Подсчет количества переходов из 1 ®0 в восьмиразрядном слове.

Текст программы:

|

Адрес команды |

Адрес перехода |

Тип перехода |

Приёмник |

Источник |

Функция АЛУ |

А |

В |

Д |

Выполняемое действие |

|

0000 |

xxxx |

0010 |

x000 |

x111 |

0000 |

xxxx |

xxxx |

Дм |

Загрузка младшего полубайта |

|

0001 |

xxxx |

0010 |

x011 |

x111 |

0000 |

xxxx |

0000 |

Дс |

Загрузка старшего Полубайта |

|

0010 |

xxxx |

0010 |

x011 |

x111 |

0000 |

xxxx |

0011 |

0 |

Обнуление счётчика Переходов ( РОН3 ) |

|

0011 |

xxxx |

0010 |

x011 |

x111 |

0000 |

xxxx |

0100 |

7 |

Инициализация счётчика цикла (РОН4) |

|

0100 |

xxxx |

0010 |

x011 |

x100 |

0000 |

0000 |

0001 |

xxxx |

Запись РОН0 в РОН1 |

|

0101 |

xxxx |

0010 |

1110 |

1011 |

х011 |

xxxx |

0000 |

xxxx |

Арифм. Сдвиг (РОН0,Q) влево |

|

0110 |

xxxx |

0010 |

x011 |

x001 |

х101 |

0000 |

0001 |

xxxx |

Запись ( РОН1 & ! РОН0 ) в РОН1 |

|

0111 |

1011 |

1101 |

x001 |

x011 |

0000 |

xxxx |

0001 |

xxxx |

Переход по знаку РОН1 |

|

1000 |

xxxx |

0010 |

x011 |

x011 |

0001 |

xxxx |

0100 |

xxxx |

Декремент счётчика цикла |

|

1001 |

0100 |

0000 |

x001 |

x011 |

0000 |

xxxx |

0100 |

xxxx |

Возврат пока счётчик цикла не равен 0 |

|

1010 |

1010 |

0001 |

x001 |

x011 |

0000 |

xxxx |

0011 |

xxxx |

Вывод числа переходов и останов |

|

1011 |

1000 |

0001 |

x011 |

x011 |

1000 |

xxxx |

0011 |

xxxx |

Инкремент счётчика переходов и возврат |

9. Выводы.

В данном цикле работ был исследован микропроцессор МП1804, исследованы возможности процессора, выполнены индивидуальные задания.

Необходимо упомянуть о достоинствах и недостатках исследованного процессора. К достоинствам можно отнести такие свойства, как: относительно простая структура; система команд, содержащая относительно большое количество команд арифметических операций; относительно удобный способ ввода и отладки программ. К недостаткам же, в первую очередь, относится то, что микропрограммная память составляет только 16 микрокоманд (разрядностью 32), что не позволяет составлять длинные микропрограммы. Это проблему можно решить, используя несколько блоков центрального процессора и блока микропрограммного управления (например, К1804ВУ1). Необходимая разрядность при этом достигается за счет объединения

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.