6.Особенности функционирования суперконвейерных архитектур.

Конвейерная архитектура

Конвейерная архитектура (pipelining) была введена в центральный процессор с целью повышения быстродействия. Обычно для выполнения каждой команды требуется осуществить некоторое количество однотипных операций, например: выборка команды из ОЗУ, дешифрация команды, адресация операнда в ОЗУ, выборка операнда из ОЗУ, выполнение команды, запись результата в ОЗУ. Каждую из этих операций сопоставляют одной ступени конвейера. Например, конвейер микропроцессора с архитектурой MIPS-I содержит четыре стадии:

получение и декодирование инструкции (Fetch);

адресация и выборка операнда из ОЗУ (Memory access);

выполнение арифметических операций (Arithmetic Operation);

сохранение результата операции (Store).

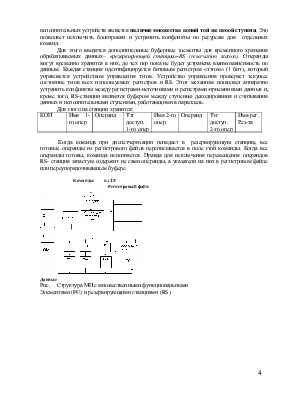

После освобождения k-й ступени конвейера она сразу приступает к работе над следующей командой. Если предположить, что каждая ступень конвейера тратит единицу времени на свою работу, то выполнение команды на конвейере длиной в n ступеней займёт n единиц времени, однако в самом оптимистичном случае результат выполнения каждой следующей команды будет получаться через каждую единицу времени.

Действительно, при отсутствии конвейера выполнение команды займёт n единиц времени (так как для выполнения команды по прежнему необходимо выполнять выборку, дешифрацию и т. д.), и для исполнения m команд понадобится m*n единиц времени; при использовании конвейера (в самом оптимистичном случае) для выполнения m команд понадобится всего лишь n + m единиц времени.

Факторы, снижающие эффективность конвейера:

простой конвейера, когда некоторые ступени не используются (напр., адресация и выборка операнда из ОЗУ не нужны, если команда работает с регистрами);

ожидание: если следующая команда использует результат предыдущей, то последняя не может начать выполняться до выполнения первой (это преодолевается при использовании внеочередного выполнения команд, out-of-order execution);

очистка конвейера при попадании в него команды перехода (эту проблему удаётся сгладить, используя предсказание переходов).

Некоторые современные процессоры имеют более 30 ступеней в конвейере, что увеличивает производительность процессора, однако приводит к большому времени простоя (например, в случае ошибки в предсказании условного перехода).

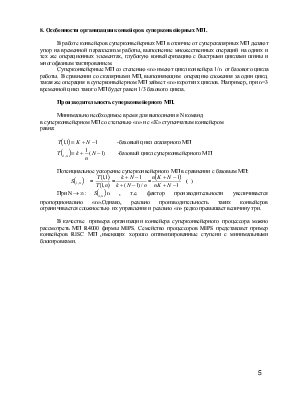

Суперконвейеризация, или разбиение конвейера на большое(!) число стадий, позволяет делать за один цикл меньше, притом, что снаружи все выглядит так, что процессор делает все тот же объем работы за один цикл. Увеличение стадий конвейера сопровождается упрощением стадий., а чем проще стадии, чем меньше время их выполнения, что и позволяет наращивать тактовую частоту.

Современные микропроцессоры содержат десять, 11 и более обрабатывающих устройств, каждое из которых представляет собой конвейер. Казалось бы, при увеличении числа исполнительных устройств и числа ступеней конвейера нетрудно обеспечить любую наперед заданную скорость исполнения программы. К сожалению, подобного повышения производительности можно добиться только в программах, не содержащих циклов и команд ветвления, однако таких программ с последовательной структурой кода практически не существует: средне статистически линейные участки программ редко содержат больше 3 - 5 параллельных команд. Следовательно, конвейеризация и суперконвейеризация, направленные на повышение производительности процессора, эффективны только для последовательной структуры кода программы. Большая частота ветвлений делают задачу распределения потока команд по ступеням конвейера крайне сложной. Характерными примерами суперконвейерных компьютеров является семейство МП фирмы MIPS-R4000, R8000, R10000.

Специфические вопросы построения конвейерных и суперконвейерных систем должна охватывать рассмотрение следующих разделов:

-предвыборку команд;

-внутреннее продвижение данных;

-программную блокировку команд и данных;

-аппаратные методы техники «табло»;

-взаимозависимость по данным:

-технику ветвлений;

-технику очередей команд;

-организацию КЭШей команд и данных и др. вопросы.

//думаю, этот список тоже входит в особенности, но поскольку все это будет рассмотрено в других вопросах, бессмысленно писать об этом и здесь тоже. Так что имейте в виду J

Маша

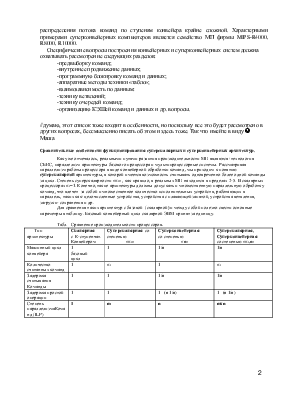

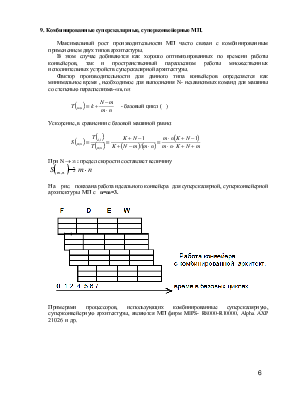

Сравнительные особенности функционирования суперскалярных и суперконвейерных архитектур.

Как уже отмечалось, реальными путями развития производительности МП являются: технология СБИС, параллелизм архитектуры базового процессора и мультипроцессорные системы. Рассматривая параллелизм работы процессора в виде конвейерной обработки команд, мы приходим к понятию суперскалярной архитектуры, в которой имеется возможность считывать одновременно более одной команды за цикл. Степень суперскалярности «m» , как правило, в реальных МП находится в пределах 2-5. В скалярных процессорах m=1. Конечно, такие архитектуры должны допускать и множественную параллельную обработку команд, что влечет за собой и множественное количество исполнительных устройств, работающих в параллель, таких как: целочисленные устройства, устройства с плавающей запятой, устройства ветвления, загрузки- сохранения и др.

Для сравнения таких архитектур с базовой (скалярной) и между собой полезно свести основные параметры в таблицу. Базовый конвейерный цикл скалярной ЭВМ принят за единицу.

Табл. Сравнение производительности процессоров.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.