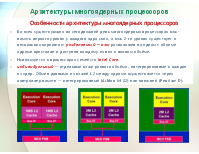

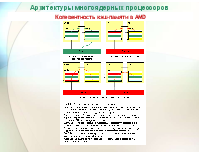

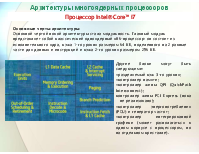

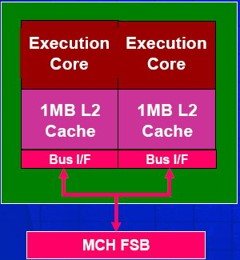

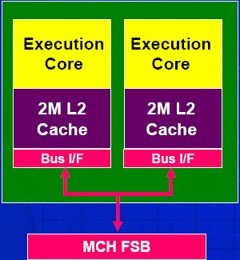

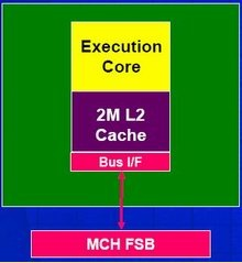

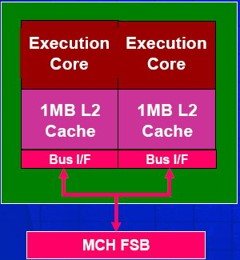

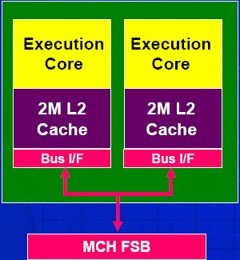

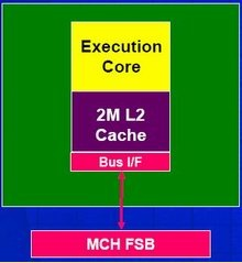

- всех существующих на сегодняшний день многоядерных процессорах кэш-память первого уровня у каждого ядра своя, а кэш 2-го уровня существует в нескольких вариантах: разделяемый — кэш расположен на одном с обоими ядрами кристалле и доступен каждому из них в полном объёме.

-

Используется в процессорах семейств Intel Core.

-

индивидуальный — отдельные кэши равного объёма, интегрированные в каждое из ядер. Обмен данными из кэшей L2 между ядрами осуществляется через контроллер памяти — интегрированный (Athlon 64 X2) или внешний (Pentium D).

Архитектуры многоядерных процессоров

Особенности многоядерных архитектур

Архитектуры многоядерных процессоров

Особенности многоядерных архитектур

Архитектуры многоядерных процессоров

Особенности многоядерных архитектур

-

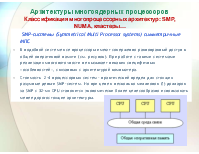

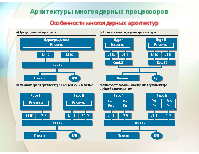

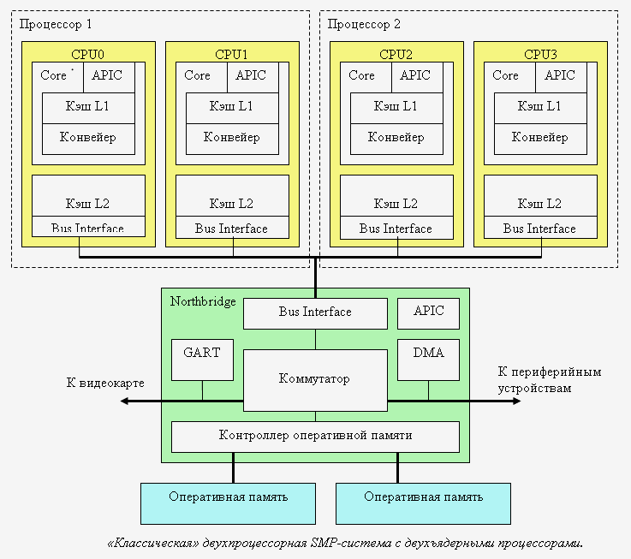

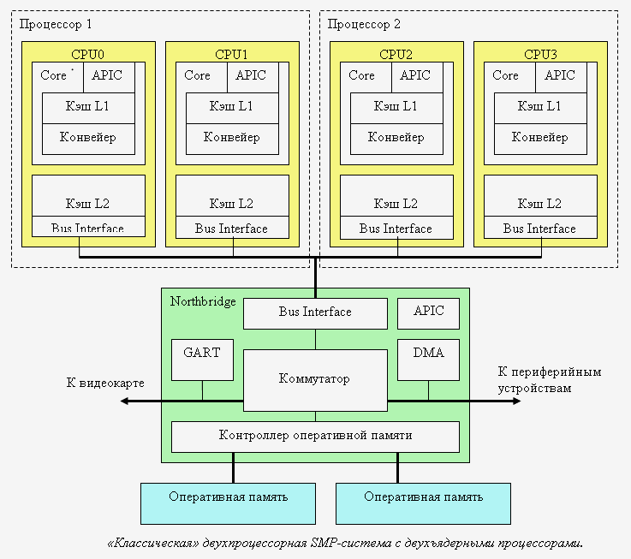

Архитектура таких МП традиционна. В ней есть несколько «равноправных» центральных процессоров (как правило, разделяющих общую шину); есть оперативная память и есть периферия различного быстродействия.

-

Весь комплект объединяется в единое целое специальным коммуникационным процессором – «северным мостом» (Northbridge) чипсета. Через него проходят все потоки данных (видео, памяти, периферии)

-

Подобный «централизованный» подход, во-первых, отличается относительной простотой, а во-вторых, удобен тем, что в нём каждый компонент компьютера получается узкоспециализированным, и поддающимся модернизации независимо от других компонентов.

-

Т.о. с одним и тем же Northbridge можно использовать различные по своей производительности средства и ,наоборот, – меняя Northbridge, можно использовать с одним и тем же процессором совершенно разные по скорости типы оперативной памяти..

Архитектуры многоядерных процессоров

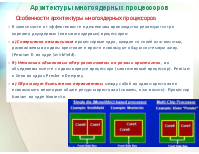

APIC (Advanced Programmable Interrupt Controller) – программируемый контроллер прерываний

-

Его «классическая» задача: они позволяют процессору быстро реагировать на запросы прерываний (аппаратных и программных прерываний - exceptions).

-

Реакция на каждое из прерываний задается вектором прерываний – набором адресов в памяти, описывающих «что делать дальше» процессору в случае возникновения прерывания: какие обработчики прерывания необходимо выполнять.

-

В случае многопроцессорных, многоядерных (и даже в случае процессоров с Hyper-Threading!) требуется обеспечить контроллерами каждое ядро процессора (включая каждое виртуальное ядро в

-

Pentium 4 c Hyper-Threading), обрабатывающих «программные прерывания.

-

Кроме того, необходим еще один, «синхронизирующий» APIC в чипсете, который обеспечивает обработку аппаратных прерываний и, занимается «рассылкой» программных прерываний в тех случаях, когда возникшее на одном процессоре прерывание почему-то затрагивает и остальные процессоры.

Архитектуры многоядерных процессоров

DMA (Direct Memory Access) – контроллер прямого доступа к памяти

-

DMA – это такой своеобразный «альтернативный процессор», который занимается в процессоре обработкой «фоновых» задач, связанных с периферией.

-

Например, пересылкой данных с жесткого диска. Для этого ЦП пересылает запрос в DMA-контроллер, чтобы тот выполнил эту задачу за него, и переключиться, пока этот запрос выполняется, на какую-нибудь другую задачу.

-

Контроллер играет центральную роль в интерфейсе Ultra ATA ( Advanced Technology Attachment — присоединение по передовой технологии) — параллельный интерфейс подключения накопителей: жёстких дисков и оптических приводов к компьютеру).

Архитектуры многоядерных процессоров

GART (Graphical Address Relocation Table)- таблицы отображения адресов графических адаптеров

-

GART (Graphical Address Relocation Table) часть механизма работы с с шиной AGP.

-

AGP (Accelerated Graphics Port, ускоренный графический порт) — разработанная в 1997 году компанией Intel, специализированная 32-битная системная шина для видеокарты.

-

Например, шина AGP 8x (спецификация AGP 3.0) передаёт 8 блоков за один такт, таким образом, пропускная способность шины достигает 2 ГБ/с.

-

При работе AGP использует два режима: DMA –ПДП и DME (Direct Memory Execute) — в этом режиме основная и видеопамять находятся как бы в общем адресном пространстве. Общее пространство эмулируется с помощью таблицы отображения адресов ( Graphic Address Remapping Table, GART) блоками по 4 Кб. Таким образом копировать данные из основной памяти в видеопамять уже не требуется, этот процесс называют AGP-текстурированием.

-

Т.о. GART обеспечивает графическому ускорителю доступ к системной памяти процессора – реализация механизма виртуальной памяти для GPU, то есть отображение «линейного» адресного пространства, с которым работает ускоритель, на «реальное», произвольным образом «перетасованное» с «обычными данными».

-

Позволяет современным 3D-ускорителям использовать не только видеопамять контроллера, но и «основную» системную память компьютера.

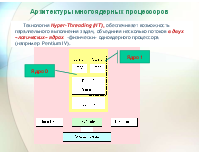

Архитектуры многоядерных процессоров

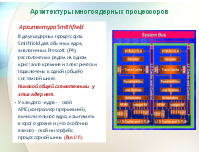

AMD Toledo с интегрированным Northbridge

-

Архитектура AMD K8 отличается от «интеловской»: она концептуально иная, поскольку в ней отсутствует выделенный центр.

-

Каждый из процессоров архитектуры AMD64 является независимой и «самодостаточной» единицей, объединяющей в себе почти всю функциональность северного моста традиционных наборов системной логики.

-

На блок-схеме представлена двухпроцессорная система на базе двухъядерных AMD Opteron. Вся функциональность северного моста интегрирована в центральный