1.4. Синтез мультиплексора

В качестве преобразователя параллельной формы представления числа в последовательную будем использовать мультиплексор.

Мультиплексор это функциональный узел, осуществляющий коммутацию одного из нескольких входов данных к выходу. Номер выбранного входа соответствует коду поданному на адресные входы мультиплексора . Исходя из синтеза счётчика, мультиплексор будет иметь шесть информационных D - входа и три адресных А - входа. Так как должно соблюдаться следующее соотношение:

ND £ 2NA , где ND - количество информационных входов.

NA - количество адресных входов.

Так же мультиплексор будет иметь стробирующий вход.

Набор переменных, поступающих на адресные входы мультиплексора, задаёт двоичное число Ni вида A0, A1,A2 . При подаче сигнала на стробирующий вход, выходная переменная - Y повторяет переменную информационного входа DNi с номером Ni .

|

|

Выход |

||||

|

А1 |

А2 |

А3 |

Q |

||

|

0 |

0 |

0 |

D0 |

||

|

0 |

0 |

1 |

D1 |

||

|

0 |

1 |

0 |

D2 |

||

|

0 |

1 |

1 |

D3 |

||

|

1 |

0 |

0 |

D4 |

||

|

1 |

0 |

1 |

D5 |

||

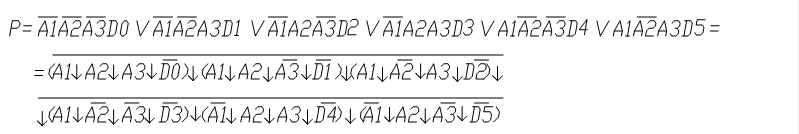

Следовательно, логическое выражение для выхода Y мультиплексора будет иметь вид:

|

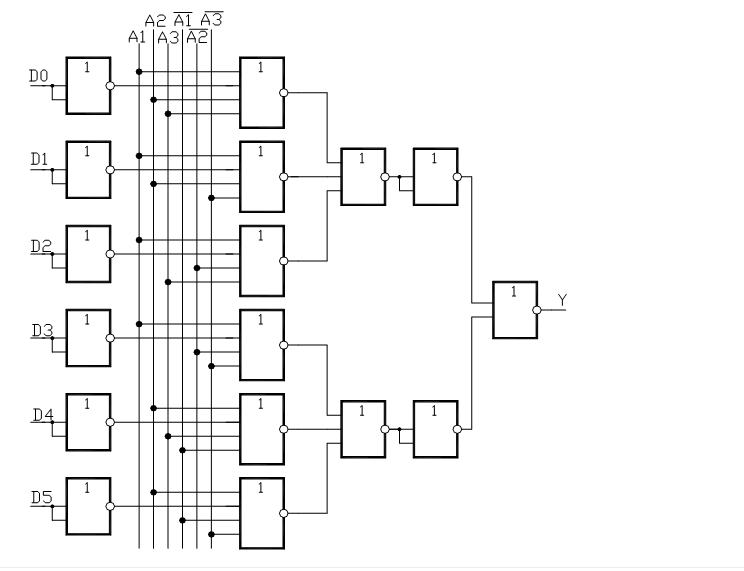

Схема мультиплексора изображена на рис. 1.4.1.

|

Для последовательного изменения адресного кода от состояния 000 до 101 мы должны синтезировать двоичный, суммирующий счётчик с коэффициентом счёта ксч = 6, используя заданную элементную базу. Составим таблицу изменения состояний триггеров счётчика.

Таблица 1.4.2. Таблица изменения состояний триггеров счётчика.

|

№ входящего импульса |

Q3 |

Q2 |

Q1 |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

|

2 |

0 |

1 |

0 |

|

3 |

0 |

1 |

1 |

|

4 |

1 |

0 |

0 |

|

5 |

1 |

0 |

1 |

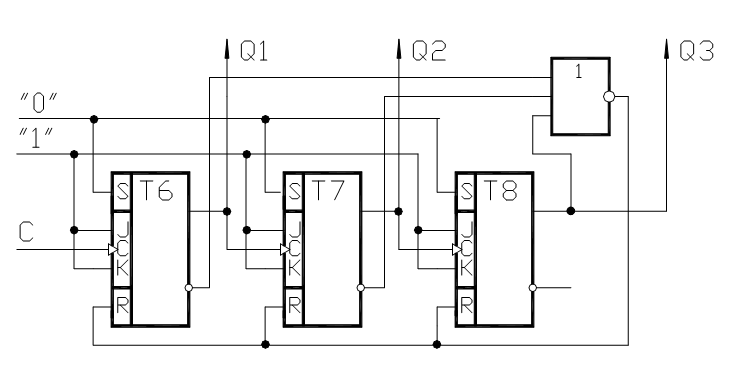

Согласно полученной таблице, построим схему счётчика. Функциональная схема счётчика, для управления адресными входами мультиплексора приведена на рис. 1.4.2.

|

|

Так как разрабатываемый мультиплексор имеет шесть информационных входов, то он (мультиплексор) должен работать в шесть раз быстрее остальных элементов дискретного устройства. Для этой цели между генератором тактовых импульсов и остальной частью дискретного устройства устанавливается делитель частоты на шесть. Данный делитель частоты построен на двоичном счётчике с последовательным переносом с коэффициентом счёта равным шести. Т. о. в качестве делителя частоты на шесть будем использовать разработанный счётчик для управления адресными входами мультиплексора. При этом в качестве выхода делителя частоты будет использоваться прямой выход триггера Т8.

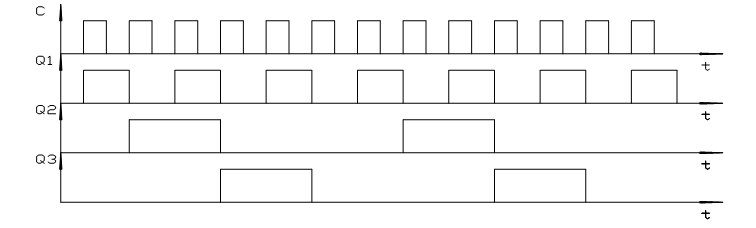

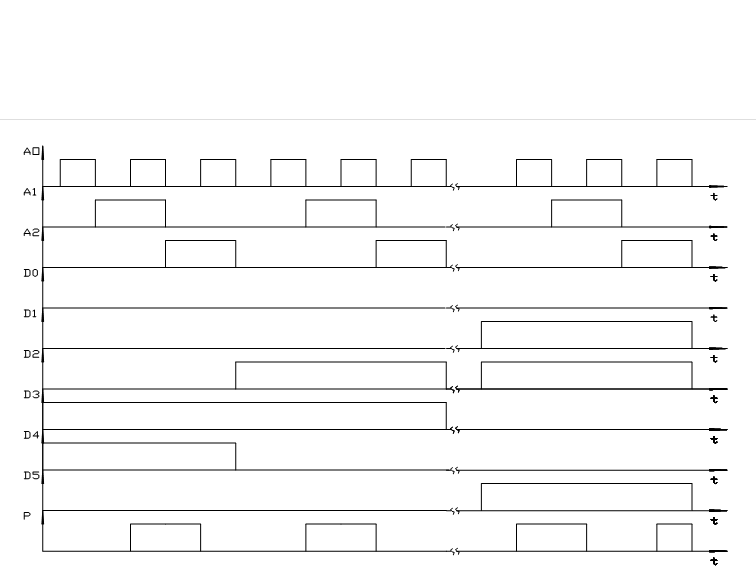

Импульсно - временная диаграмма выходного

сигнала делителя частоты показана на рис. 1.4.3, а мультиплексора – на рис.

1.4.4.

|

||||

|

||||

Рисунок 1.4.4. Импульсно-временная диаграмма работы мультиплексора.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.