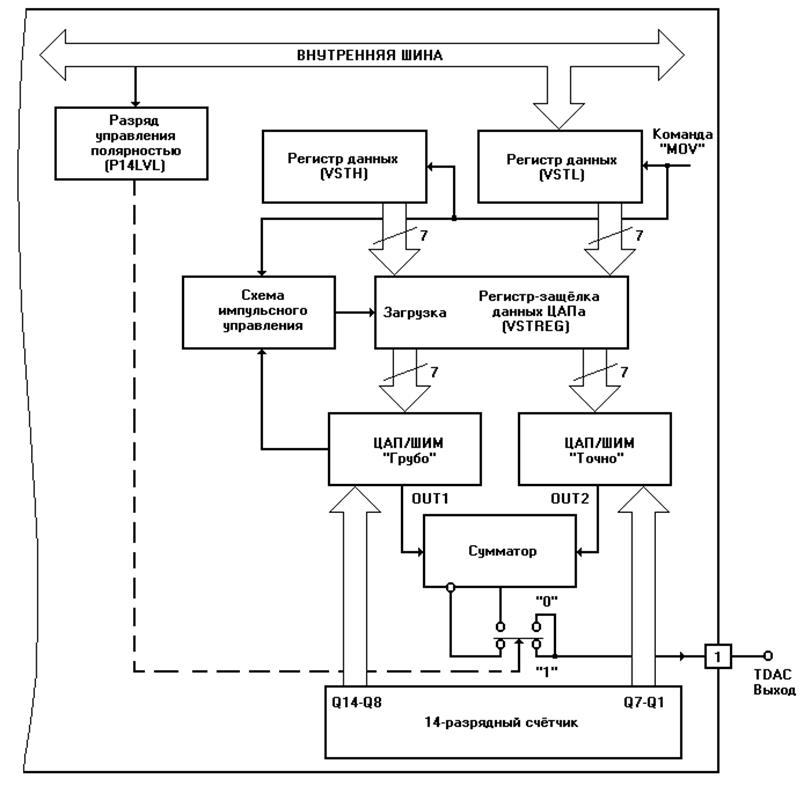

(См. Рис. 9):

1. Два 7-разрядных регистра-защелки интерфейса (VSTH;VSTL)

2. Один 14-разрядный регистр-защелка данных для ЦАП (VSTREG)

3. Два 7-разрядных ЦАПа ("Грубо" и "Точно")

4. Сумматор

5. 14-разрядный счетчик

6. Схема импульсного управления.

14-разрядный

счетчик непрерывно работает в последовательном режиме с частотой тактирования ![]() . Период тактирования

. Период тактирования

Период

повторения для одного полного цикла работы 14-разрядного счетчика: ![]() . Период повторения для одного полного цикла работы младших семи

разрядов счетчика:

. Период повторения для одного полного цикла работы младших семи

разрядов счетчика: ![]() .

.

Следовательно

число периодов ![]() в полном цикле

в полном цикле ![]() будет:

будет:

;

;

Для гарантии

правильной работы схемы первым загружается регистр-защелка данных VSTH, затем

- регистр-защелка данных VSTL Содержимое VSTH используется для предварительной

(грубой) настройки, а содержимое VSTL - для точной подстройки. В начале первого

периода tsub, следом за загрузкой VSTL, оба регистра-Защелки данных

разгружаются в регистра VSTREG; требуется один период ![]() , для формирования соответствующей последовательности импульсов. Для

обеспечения надежной работы и требуемой точности преобразования ЦАП

целесообразно пропустить два периода

, для формирования соответствующей последовательности импульсов. Для

обеспечения надежной работы и требуемой точности преобразования ЦАП

целесообразно пропустить два периода ![]() , прежде чем начинать новую последовательность.

, прежде чем начинать новую последовательность.

Грубая настройка.

Выход грубой

настройки OUT1 (См. Рис. 9) выдает сигнал сброса (НИЗКИЙ уровень напряжения в

неактивном состоянии) в начале каждого периода ![]() : Уровень напряжения остается НИЗКИМ до тех пор, пока не закончится временной

интервал

: Уровень напряжения остается НИЗКИМ до тех пор, пока не закончится временной

интервал ![]() , а затем происходит переключение на ВЫСОКИЙ уровень, который остается

неизменным до начала следующего периода

, а затем происходит переключение на ВЫСОКИЙ уровень, который остается

неизменным до начала следующего периода ![]()

(См. Рис. 10).

Рис. 9. Блок-схема 14-разрядного ЦАП/ШИМ

2.4 ТОЧНАЯ НАСТРОЙКА

Точная настройка

достигается путем формирования дополнительных импульсов в начале конкретных

подпериодов. Длительность этих импульсов равна ![]() . Подпериод, в котором добавляется импульс, определяется содержимым

регистра-защелки данных VSTL.

. Подпериод, в котором добавляется импульс, определяется содержимым

регистра-защелки данных VSTL.

В таблице 3 приведены номера подпериодов в начале которых формируется дополнительный импульс, в зависимости от положения нулевого бита VSTL. При нескольких нулевых битах формируется сочетание дополнительных импульсов. Например, если VSTL= 1111010, дополнительные импульсы будут сформированы в подпериодах 16,48, 64, 80 и 112 (См. Рис. 11).

Таблица 3. Распределение дополнительных импульсов

|

Младшие 7 разрядов (VSTL) |

Дополнительные импульсы в подпериоды |

|||

|

1 |

1 |

1 1 1 |

1 0 |

64 |

|

1 |

1 |

1 1 1 |

0 1 |

32,96 |

|

1 |

1 |

1 1 0 |

1 1 |

16,48,80,112 |

|

1 |

1 |

1 0 1 |

1 1 |

8,24,40,56,72,88, 104. 120 |

|

1 |

1 |

0 1 1 |

1 1 |

4, 12, 20, 28, 36, 44, 52 ... 1 16, 124 |

|

1 |

0 |

1 1 1 |

1 1 |

2, 6, 10, 14, 18, 22, 26 ... 122, 126 |

|

0 |

1 |

1 1 1 |

1 1 |

1,3,5,7,9, 11, 13, 15... 125, 127 |

Рис. 10. Временная диаграмма выходного сигнала

грубой настройки (OUT1 на Рис. 9)

Рис. 11. Временная диаграмма выходного сигнала

2.5 Работа стенда.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.