МИКРОКОНТРОЛЛЕР АТ89С51 ФИРМЫ ATMEL

Данный справочный материал продолжает описание микроконтроллеров фирмы ATMEL II. 2]. КМОП- микроконтроллер АТ89С51 (далее МК) является прибором широкого применения, основанного на архитектуре MCS-51фирмы INTEL. Практически АТ89С51 представляет собой основном микроконтроллер клона, основанного на данной архитектуре. Характеристики МК в общих чертах приведены в (1).

АТ89С51 имеет в основе процессорное ядро, совместимое с контроллерами семейства MCS-51, с 8-разрядной шиной данных и адресным пространством 64 Кб (65536 байтов). Процессорное ядро и периферия имеют малый ток потребления в активном (не более 20 мА при тактовой частоте 12 МГц и напряжении питания 5 в) и "ждущем" (Idle Mode) режим (5 мА). Встроенное электрически перепрограммируемое PLASH ПЗУ (EEPROM) имеет емкость 4 Кб и допускает не менее 1000 циклов перепрограммирования (это дает возможность мобильной отладки устройств, собранных на базе АТ89С51). Записываемые в ПЗУ программы можно защитить от несанкционированного считывания двухуровневым методом защиты. Программирование осуществляется по методике, описанной ниже. В составе МК. кроме этого, имеется ОЗУ 128 байт. При снятии питающего напряжения данные в ОЗУ теряются.

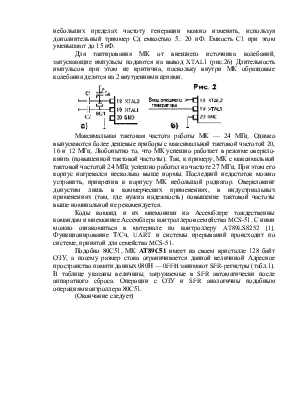

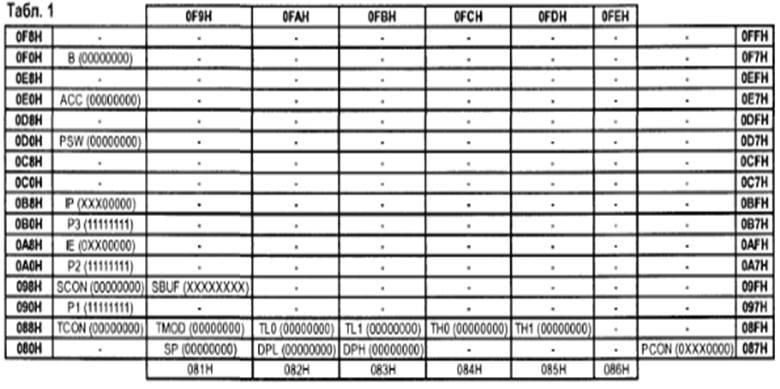

Встроенный тактовый генератор может работать на частотах до 24 МГц. нижняя рабочая частота не нормируется (т.е. она может быть равна 0 Гц). Кроме того, процессорное ядро может находиться в двух энергосберегающих режимах. В 'ждущем'' режиме работа процессора прекращается, а ОЗУ, Таймеры/счетчики (Т/Сч), полнодуплексный последовательный порт (UART) и система прерываний продолжают функционировать, в 'энергосберегающем' (Power Down Mode) режиме данные в ОЗУ и регистрах специальных функций (Special Function Registers) сохраняются, работа тактового генератора приостанавливается, а МК при этом прекращает функционировать. Во втором режиме работа МК возобновляется только после аппаратного сброса.

АТ89С51 имеет расширенную периферию. Помимо двух 16-битных Т/Сч и UART. имеются 32 программируемые линии ввода-вывода (соответствующие линиям I/O контроллера 80С51 фирмы INTEL). МК имеет "шестивекторную" систему прерываний — две линии прерываний от Т/Сч. по одной линии от UART и контроллера питающего напряжения и две линии от внешних источников прерывания INTO и INT1.

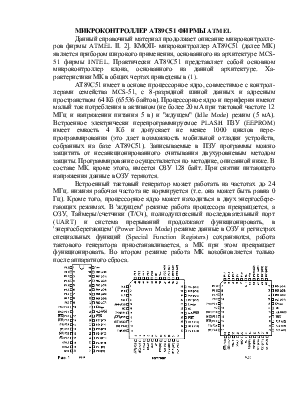

МК выпускается в корпусах трех исполнений (рис.1): традиционном 40-выводном корпусе PlasticDlP, 44-выводном корпусе POFP/TQFP и монтируемом на поверхность плат корпусе PLCC. Назначение выводов следующее:

- GND — общий провод ("минус" источника питания);

- Vсс — напряжение источника питания ("плюс") 5 В ± 20%;

- POO — Р0.7 — восьмиразрядный двунаправленный I/O порт с выходами включенными по схеме открытого стока. Когда в пинии порта записываются 1. они используются как высокоомные входы На вывод к порту можно подключить до 8 TTL-входов. Порт может быть сконфигурирован для организации мультиплексированной шины адресов/данных, используемой для доступа к внешней памяти программ и данных. В этом режиме к выходам внутренне подключаются 'подтягивающие' резисторы к шине Vсс. Порт 0 также используется для приема и передачи данных при программировании. При верификации (проверке качества программирования) также активизируются "подтягивающие" резисторы;

- Р1.0 — Р1.7 — восьмиразрядный двунаправленный I/O порт, может подключаться к 4-м TTL-выходам/входам. Когда в его линии записывают 1. он работает на ввод: к Vсс. подключаются внутренние "подтягивающие" резисторы. При программировании и верификации порт 1 используется для ввода младшего байта адреса программируемой ячейки;

- Р2.0 — Р2.7 — восьмиразрядный двунаправленный I/O порт, который также может подключаться к 4-м TTL-выходам/входам. Как порт ввода/вывода, он функционирует подобно порту 1. Порт 2 выводит старший байт адреса ячейки внешней памяти команд и данных при обращении к ней. При программировании и верификации используется для ввода старшего байта программируемой ячейки .

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.