Комментарий – описываются действие, выполняемые в данном предложении, отделяется ; , не воспринимается транслятором.

Псевдокоманды Ассемблера

Псевдокоманда – это указание транслятору. Псевдокоманды не выполняются МП. Наиболее часто используемые псевдокоманды:

ORG, END, EQU, SET, DB, DW, DS.

Псевдокоманда ORG

< Метка: > ORG Выражение

Указывает, с какого адреса начинается размещение программы, например:

ORG 100H

Если ORG отсутствует в начале программы, то по умолчанию начальный адрес программы 0000Н

Псевдокоманда END - конец

< Метка: > END

конец программы

Псевдокоманда EQU присваивает символическому имени какое – либо значение

Имя EQU выражение

Например:

CONST EQU 25H

MEM EQU 2000H

Имена, определённые командой EQU, не должны переопределяться программой.

Псевдокоманда SET(установить) позволяет переопределять имена в программе, т.е. присваивать им различные значения.

Имя SET выражение

Например:

CONST SET 25H ; Имя CONST имеет значение 25H;

………..

CONST SET 45H ; Имя CONST имеет значение 45H;

Псевдокоманда DB – определить байт

< Метка: > DB список резервирует 1 ячейку памяти и записывает в неё значение из списка.

Например:

TABLE: DB, 01H, 07H, 0ABH

Псевдокоманда DW – определить слово (2 байта)

< Метка: > DW выражение

Резервирует 2 соседние ячейки и размещает в них 2–х – байтовое число из списка

Псевдокоманда DS - определить память

< Метка: > DS выражение

Резервирует в памяти определённое число ячеек, которые определяются выражением ( при этом в выделенные ячейки никаких значений не заносится ).

Например:

ORG 1000H

Base : DS 100; резервирует 100ячеек с адреса 1000Н

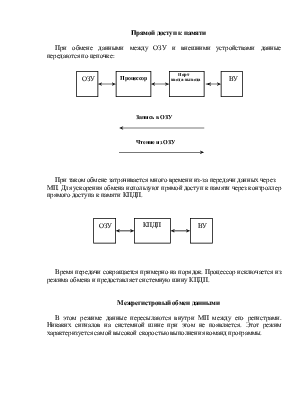

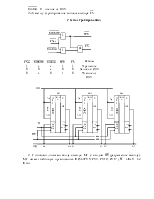

Память

![]() Base

1000

Base

1000

100 ячеек

![]()

Пример записи программы на языке Ассемблера:

; DELAY – имя подпрограммы задержки

NUM EQU 100

ORG 50H; начальный адрес программы

DELAY: MVI C, NUM

LOOP: NOP

DCR C

![]() JNZ

LOOP; цикл если ( С ) = 0

JNZ

LOOP; цикл если ( С ) = 0

RET; возврат из подпрограмы.

END; конец программы.

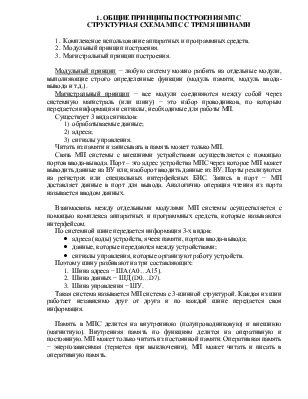

17.МЕТОДИКА РАЗРАБОТКИ ПРОГРАМНОГО ОБЕСПЕЧЕНИЯ МПС.

ОСНОВНЫЕ ТИПЫ АЛГОРИТМОВ И ИХ ПРОГРАМНАЯ РЕАЛИЗАЦИЯ.

Этапы разработки ПО:

1. Определить и проанализировать задачу.

2. Составить алгоритм решения задачи.

3. Составить структурную схему ( блок – схему ) алгоритма.

4. Записать программу на языке Ассемблера.

5. Транслировать программу в машинные коды.

6. Занести коды программы в память МПС.

7. Отладить программу.

8. Документировать программу.

На 1– ом этапе уточняются отдельные детали задачи ( на разговорном языке)

Задача разбивается на блоки.

Методы задания алгоритмов:

1. Словесный

2. Табличный метод – использование таблиц для описания ( пример – таблица истинности)

3. С помощью формул – при использовании логических схем.

4. Графический метод – задание алгоритма с помощью геометрических фигур, называемых блоками. Последовательность блоков и соединительных линий образуют структурную схему или блок – схему (БСА).

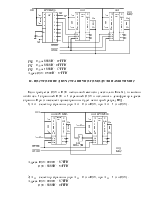

Основные блоки

![]()

![]()

|

|||||

![]()

![]()

Нет Да

![]()

![]()

![]() 1

1

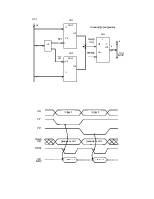

Алгоритмы делятся на виды:

1. Линейные

2. Разветвлённые

3. Циклические.

Линейные алгоритмы не содержат условий, имеют 1 ветвь обработки и изображаются линейной последовательностью связанных друг с другом блоков.

Разветвлённый алгоритм содержит 1 или несколько логических условий, может иметь несколько ветвей обработки.

Проверка условий – это проверка флагов.

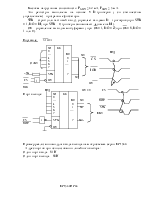

Пример: в МПС поступает 1–байтное число со знаком. Если оно положительное, то выводится в 1 –й порт, если отрицательное, то выводится во 2– й порт.

Знак числа кодируется 7-м разрядом байта и определяется флагом S.

7 6 5 4 3 2 1 0

|

S |

S = 0 – положительное

S = 1 – отрицательное

Таким образом, необходимо проверять флаг S после ввода числа из порта.

![]()

ДА НЕТ

![]()

Символические имена портов:

IPORT – порт ввода

![]() OPORT1

OPORT1

OPORT2 порты вывода

IN IPORT; ввод данных

ORA A; установка флагов

JP MET1; переход на MET1, если S = 0

OUT OPORT2; вывод

HLT

MET1: OUT OPORT1; вывод

HLT

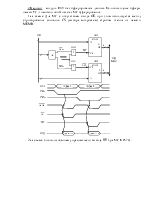

Циклические алгоритмы содержит 1 или несколько циклов. Цикл – это последовательность повторяющихся команд.

Имеется счётчик цикла и переменная цикла – показывают сколько раз должен повторяться цикл.

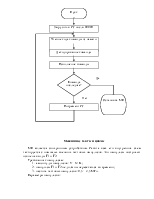

Блок – схема циклического алгоритма со счётчиком циклов:

|

Вход в цикл |

Тело цикла

|

НЕТ

![]()

ДА

|

Выход из цикла |

Если число повторений цикла N = 1…256 раз – в качестве счётчика цикла может использоваться любой из регистров МП.

Пример:

…

MVI C, NUMBER; загрузить счётчик цикла

LOOP: NOP

NOP

![]() DCR

DCR

JNZ LOOP; цикл, если ( С ) = 0

……… ;выход из цикла

Если число повторений цикла N = 1…65536 раз, то в качестве счётчика цикла можно использовать регистровую пару BC, DE, HL .

Однако при этом возникает проблема проверки окончания цикла, т.е. проверки на ноль содержания регистровой пары. Дело в том, что программа декремента регистровой пары DCX не влияет на флаги МП и проверить на ноль пару по флагу Z невозможно.

Имеется два варианта проверки:

1. Сначала проверяется на ноль старший регистр пары, а потом младший.

Например, для пары ВС:

LXI B, NUMBER

LOOP: NOP

NOP

DCX B

MOV A, B

![]() CPI 0

CPI 0

JNZ LOOP; цикл, если ( В ) = 0

MOV A, C

CPI 0

![]() JNZ LOOP; цикл, если ( С ) = 0

JNZ LOOP; цикл, если ( С ) = 0

…….. ; выход из цикла

2. Для проверки на ноль используется логическая команда ORA (операция ИЛИ) содержимого регистров пары. Результат выполнения команды будет равным нулю, т.е. установится Z = 1, только тогда, если оба регистра пары равны нулю.

Например, для пары ВС:

LXI B, NUMBER

LOOP: NOP

NOP

DCX B

MOV A, B

![]()

![]() ORA

C

ORA

C

JNZ LOOP; цикл, если ( В ) = 0 и ( C ) = 0

……… ; выход из цикла

Второй вариант короче, поэтому эффективнее.

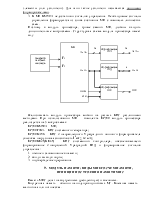

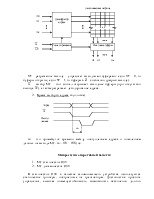

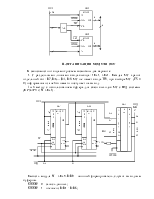

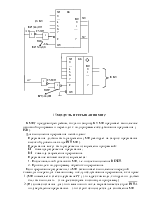

18.БИС ПАРАЛЕЛЬНОГО ИНТЕРФЕЙСА КР580ВВ55А : ОСНОВНЫЕ ХАРАКТЕРИСТИКИ, ВНУТРЕННЯЯ СТРУКТУРА, ПОДКЛЮЧЕНИЕ К СИСТЕМНОЙ ШИНЕ МПС, ПРОГРАММИРОВАНИЕ.

Интерфейсная БИС КР580В55А является наиболее универсальным устройством ввода – вывода информации в МПС в параллельном коде. Её часто называют программируемым параллельным адаптером

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.