Все ошибки и флаги состояния, связанные с модулем UART сброшены, когда модуль выключен. Биты URXDA, OERR, FERR, PERR, UTXEN, UTXBRK, и UTXBF сброшены, тогда как биты RIDLE и TRMT установлены. Другие служебные биты (включая ADDEN, URXISEL <1:0> и UTXISEL <1:0>) и UxMODE и регистры UxBRG не затрагивают.

Сброс бита UARTEN, в то время как UART активен, прервет все передачи, ждущие обработки, и сбрасывают модуль как определено выше. Перевключение UART перезапустит UART в той же самой конфигурации.

5. Передатчик UART

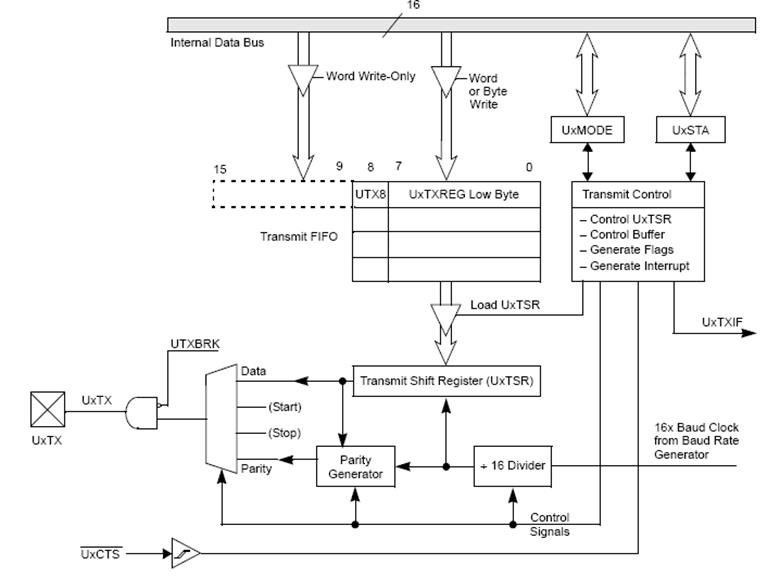

Блок-схема передатчика UART показана на рисунке 3. Основа передатчика – это передающий сдвиговый регистр (UxTSR). Сдвиговый регистр получает данные из передающего буфера FIFO, регистра UxTXREG. Регистр UxTXREG загружается данными из программы. UxTSR регистр не загружается пока Стоповый бит не был передан от предыдущей загрузки. Как только Стоповый бит будет передан, UxTSR загружается новыми данными из регистра UxTXREG (если доступен).

Обратите внимание: регистр UxTSR не отображен в памяти данных, так что он не доступен пользовательскому приложению.

Рисунок 3. Блок схема передатчика UART

Передача включается путём установки бита UTXEN (UxSTA <10>). Фактическая передача не будет происходить до тех пор пока регистр UxTXREG не будет загружен данными и генератор Baud Rate (UxBRG) изменяется (Рисунок 3). Обычно, когда передача является первой, регистр UxTSR пуст, так передав в регистр UxTXREG, приводит немедленная передача в регистр UxTSR. Очистка бита UTXEN в течение передачи вызовет отмену передачи и сбросит передатчик. В результате, UxTX вывод возвратится в состояние высокого импеданса.

Чтобы выбирать 9-ти битную передачу, биты PDSEL <1:0> (UxMODE <2:1>) должны быть установлены на ‘11’ и девятый бит должен быть записан в бит UTX8 (UxTXREG <8>). Запись слова должна быть выполнена для UxTXREG так, чтобы все девять битов были написаны одновременно.

Обратите внимание: В случае передачи 9-ти битных данных чётность не применяется.

При сбросе микроконтроллера, вывод UxTX конфигурируется как вход, поэтому, состояние вывода UxTX не определено. Когда модуль UART включён, передающий вывод управляется высоким уровнем. Это состояние остается до тех пор пока не записаны данные в передающий буфер (UxTXREG). Передающий вывод управляется низким уровнем поскольку первые данные записаны в регистр UxTXREG. Чтобы гарантировать обнаружение стартового бита, рекомендуется иметь задержку между включением UARTx (UARTEN = 1) и инициализизации первый передачи. Задержка зависит от Baud Rate и должна быть равна или больше чем требуется времени, чтобы передать один информационный разряд.

Рисунок 4. UART передача

1 - Модуль UARTа включён (UARTEN = 1).

2- Данные записываются в передающий буфер (UxTXREG), чтобы начать передачу.

5.1. Буфер передатчика (UxTXREG)

Буфер передатчика шириной в 9 битов и глубиной в 4 уровня. Вместе с передающим сдвиговым регистром (UxTSR), пользователь фактически имеет буфер глубиной в 5 уровней. Данный буфер организован как FIFO (первый вошёл первый вышел). Как только содержимое UxTXREG передано в регистр UxTSR, текущее расположение указателя буфера становится доступным для новых данных, которые будут записаны, и указатель в буфере снова переместится. Бит состояния UTXBF (UxSTA <9>) устанавливается всякий раз, когда буфер полон. Если пользователь пытается записывать в полный буфер, новые данные не будут приняты в FIFO.

FIFO сбрасывается при любом Сбросе микроконтроллера, но не изменяется, когда микроконтроллер входит в энергосберегающий режим или пробуждается из режима энергосбережения.

5.2. Прерывание передатчика

Флаг прерывания передатчика (UxTXIF) расположен в соответствующем регистре статуса флага прерывания (IFS). Биты управления UTXISEL <1:0> (UxSTA <15,13>) определяют, когда UART будет генерировать переданное прерывание.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.