5. СОСТАВЛЕНИЕ ПРИНЦИПИАЛЬНОЙ ЭЛЕКТРИЧЕСКОЙ СХЕМЫ УСТРОЙСТВА

5.1 Разработка функциональной схемы устройства

5.2 Разработка блока преобразования

Использование в качестве входных сигналов квадратурных компонент РЛ сигнала с выхода аналогового КФД приводит к необходимости преобразования их в цифровую форму с помощью двух аналого-цифровых преобразователей (АЦП). Предполагается, что амплитуда входного сигнала составляет от 0 до +5 В.

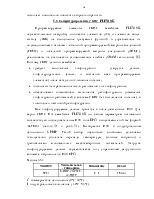

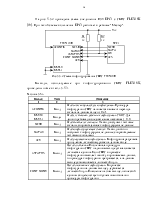

Исходя из технического задания на дипломное проектирование: разрядность входного цифрового сигнала, подаваемого на блок обработки, составляет 12 бит; частота дискретизации fд=7 МГц (t=0,142 мкс.) - это максимальная частота следования выходного сигнала с блока преобразования выбираются наиболее подходящие АЦП. Из набора отечественных АЦП [20] были рассмотрены по вышеизложенным параметрам следующие АЦП: К1108ПВ2 и К572ПВ1 (А, Б, В), но время преобразования t=1/fд у них составляет 0,9 мкс. и 170 мкс. соответственно, что не подходит к требованиям ТЗ. Из импортных АЦП [21, 18] по близким параметрам были найдены микросхемы фирм MAXIM (MAX 163, MAX 164, MAX 167 и MAX 172) и ANALOG DEVICE (AD9221, AD9223 и AD9220). На основе сравнения параметров выбранных АЦП, удовлетворяющим требованиям, признан АЦП AD9220 [18], схема включения которого приведена там же. Частота дискретизации данного АЦП равна 10 МГц, температурный диапазон составляет от –40 до +85°С, питание производится от одного источника на +5 В, динамический диапазон 86 дБ, максимальная амплитуда сигнала на входе равна +6,5 В.

5.3 Выбор элементной базы

До последнего времени системы обработки информации разделялись на системы с аппаратурной реализацией алгоритма обработки и на системы с программной обработкой.

Аппаратурная реализация связана с большими затратами на разработку, как стоимостными, так и временными. К тому же устройство обработки обладает большими массогабаритными показателями.

Таких недостатков лишена система с программной обработкой. Однако отрицательной стороной программного способа построения системы обработки является низкое быстродействие.

Современная обработка сигналов в последнее время все сильнее взаимодействует с технологией сверхбольших интегральных схем (СБИС). Из-за непрерывно возрастающих требований к скорости процесса обработки сигналов приходиться прибегать к огромным вычислительным ресурсам. Быстродействующие СБИС с высокой плотностью компоновки элементов стали все чаще делать реальными такие супервычисления. В результате технология СБИС открыла много новых перспективных направлений в обработке сигналов, ускорив наступление новой эпохи в обработке сигналов – эпохи СБИС. За последние несколько лет в мире произошел гигантский рост научных и прикладных исследований по применению СБИС в различных областях обработки сигналов.

Для использования СБИС в системах обработки сигналов важно иметь основные представления о вычислительных и архитектурных потребностях современной техники обработки сигналов, а также о потенциальных возможностях и ограничениях СБИС и технологии автоматизированного проектирования.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.