28

Для

реализации логической функции ![]() с учетом

инвертирования переменных потребуется _ ЛЭ 2ИЛИ-НЕ

с учетом

инвертирования переменных потребуется _ ЛЭ 2ИЛИ-НЕ

1) 2

2) 3

3) 5

4) 6

29

Логическая функция _ равна х1:

1)

![]()

2)

![]()

3)

![]()

4)

![]()

30

Логическая функция _ равна х3:

1)

![]()

2)

![]()

3)

![]()

4)

![]()

31

Склеиваются минтермы:

1)

![]()

2)

![]()

3)

![]()

4)

![]()

32

Логическая

функция ![]() записана в форме:

записана в форме:

1) СДНФ

2) ДНФ

3) СКНФ

4) КНФ

33

Логическая

функция ![]() записана в форме:

записана в форме:

1) СДНФ

2) СКНФ

3) КНФ

4) ДНФ

34

Логическая

функция ![]() записана в форме:

записана в форме:

1) СДНФ

2) СКНФ

3) ДНФ

4) КНФ

35

Логическая функция _ представлена в базисе «Штрих Шеффера»:

1)

![]()

2)

![]()

3)

![]()

4)

![]()

36

Логическая функция _ представлена в базисе «Стрелка Пирса»:

1)

![]()

2)

![]()

3)

![]()

4)

![]()

37

Двоичный код на выходах приоритетного шифратора «8®3», если подать «лог 1» на входы с номерами 2 и 5 одновременно, равен:

1) 010

2) 101

3) 111

4) 011

38

Двоичный код на выходах приоритетного шифратора «8®3», если подать «лог 1» на входы с номерами 3 и 7 одновременно, равен:

1) 011

2) 100

3) 000

4) 111

39

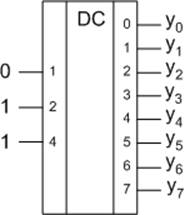

Если

на входы дешифратора «3®8» с весовыми

коэффициентами 4,2,1 подать соответственно сигналы х3=1, х2=1,

х1=0, то на выходе _ образуется минтерм ![]() :

:

1) у0

2) у3

3) у6

4) у7

40

Дешифратор «3®8» преобразует двоичный код в _ код:

1) десятичный

2) унитарный

3) с избытком 3

4) шестнадцатеричный

41

Если на информационные входы D0-D3 и на адресные входы А0-А1 мультиплексора «4®1» подать «лог 1», то на выходе образуется минтерм:

1)

![]()

2)

![]()

3)

![]()

4)

![]()

42

Мультиплексор «23®1» должен иметь _ адресных входов:

1) 1

2) 2

3) 3

4) 8

43

Мультиплексор «23®1» не может использоваться для:

1) преобразования параллельного кода в последовательный

2) коммутации на выход одного из 23 каналов

3) формирования логической функции четырех переменных

4) дешифрации адресных входов

44

Демультиплексор «1®4» не может использоваться для:

1) дешифрации адресных входов

2) преобразования двоичного кода в унитарный

3) преобразования двоичного кода в код Джонсона

4) коммутации информационного входа на один из выходов

45

На прямом выходе А¹В одноразрядного компаратора, где А и В входы, формируется функция:

1)

![]()

2)

![]()

3)

![]()

4)

![]()

46

На прямом выходе А=В одноразрядного компаратора, где А и В входы, формируется функция:

1)

![]()

2)

![]()

3)

![]()

4)

![]()

47

На выходе Р (переноса) одноразрядного полусумматора появляется «лог 1», если на входы А и В подаются сигналы:

1) А=В=0

2) А=В=1

3) А=0, В=1

4) А=1, В=0

48

На выходах S1 (суммы) и Р1 (переноса) одноразрядного комбинационного сумматора появляется «лог 1», если на входы А1, В1 (слагаемых) и Р0 (переноса) подаются сигналы:

1) А1=00, В1=1, Р0=1

2) А1=1, В1=1, Р0=0

3) А1=1, В1=0, Р0=1

4) А1=1, В1=1, Р0=1

49

При подаче на входы RS-триггера сигналов St=1, Rt=0 триггер:

1) установится в 1

2) сбросится в 0

3) изменит состояние на противоположное

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.