(ДВПИ им. В.В. Куйбышева)

Сигнальные процессоры

по дисциплине “Микропроцессоры и цифровая обработка сигналов”

для студентов специальности 201100

Разработал П.

Владивосток

2004

Применение цифровых процессоров обработки сигналов (ЦПОС) в радиотехнических системах позволяет выполнять обработку поступающей информации в реальном времени. Это означает, что все операции алгоритма обработки сигнала должны выполняться за время, не превышающее период дискретизации входного сигнала.

Отличительной особенностью сигнальных процессоров является обработка больших массивов поточной цифровой информации с высокой производительностью. Выполнение этого требования достигается за счет высокой специализации сигнальных процессоров. Для них характерно разделение шин команд и шин данных (гарвардская архитектура), аппаратная поддержка программных циклов, наличие аппаратного умножителя, включение в систему команд операции умножения с накоплением МАС (С = A * B + C) с указанным в команде правилом изменения индекса элементов массивов.

Использование однотактного умножителя и ячеек памяти в качестве операндов обуславливает относительно низкие тактовые частоты работы этих процессоров. За счет быстрого выполнения команд межрегистрового обмена Ri→Rj не удается повысить производительность вычислений, как это делается в универсальных процессорах.

Малая разрядность (32 двоичных разряда и менее) сигнальных процессоров с фиксированной запятой может привести к неустойчивости рекурсивных фильтров. Более удобными для проектирования систем обработки являются микропроцессоры с плавающей запятой, так как они не требуют выполнения операций округления и нормализации данных, контроля переполнения суммы в программе. Ведущие компании выпускают как дешевые сигнальные процессоры с фиксированной запятой, так и более дорогие процессоры с плавающей запятой.

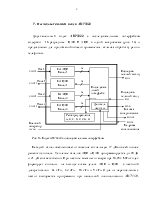

Примеры наиболее распространенных сигнальных процессоров: Motorola 56002,96002, Intel i960, Analog Devices 21xx,210xx, Texas Instruments TMS320Cxx. В курсовой работе расчет выполняется для систем, использующих сигнальный процессор ADSP-2189M (Analog Devices).

1. Структура и цели цифровой обработки аналоговых сигналов

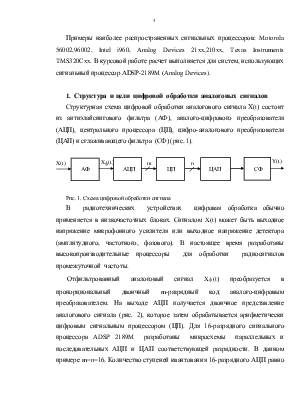

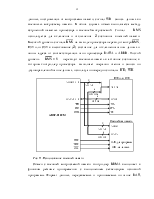

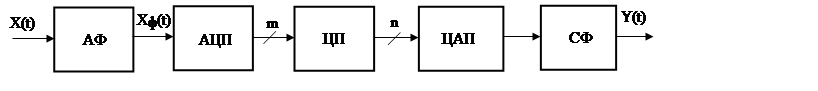

Структурная схема цифровой обработки аналогового сигнала Х(t) состоит из антиэлайсингового фильтра (АФ), аналого-цифрового преобразователя (АЦП), центрального процессора (ЦП), цифро-аналогового преобразователя (ЦАП) и сглаживающего фильтра (СФ) (рис. 1).

Рис. 1. Схема цифровой обработки сигнала

В радиотехнических устройствах цифровая обработка обычно применяется в низкочастотных блоках. Сигналом X(t) может быть выходное напряжение микрофонного усилителя или выходное напряжение детектора (амплитудного, частотного, фазового). В настоящее время разработаны высокопроизводительные процессоры для обработки радиосигналов промежуточной частоты.

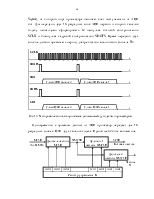

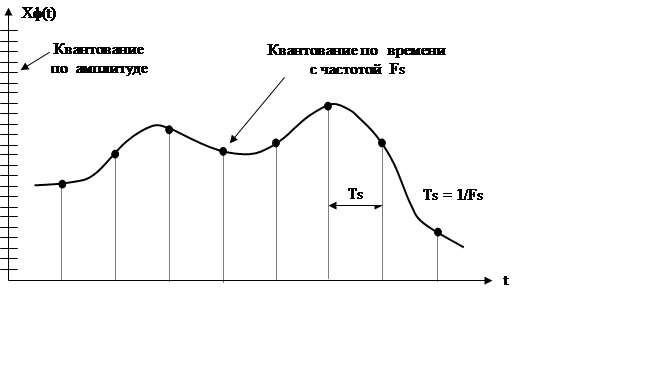

Отфильтрованный аналоговый сигнал Xф(t) преобразуется в пропорциональный двоичный m-разрядный код аналого-цифровым преобразователем. На выходе АЦП получается двоичное представление аналогового сигнала (рис. 2), которое затем обрабатывается арифметически цифровым сигнальным процессором (ЦП). Для 16-разрядного сигнального процессора ADSP 2189M разработаны микросхемы параллельных и последовательных АЦП и ЦАП соответствующей разрядности. В данном примере m=n=16. Количество ступеней квантования 16-разрядного АЦП равно 216-1= 65535. Типовые частоты квантования данного процессора составляют 8,16,32 и 64 кГц. Одно из указанных значений частоты задается в программе обработки данных при начальной инициализации процессора. Дискретные отсчеты

|

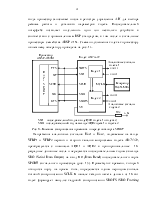

аналогового сигнала хранятся в виде массива 16-разрядных двоичных чисел в специально отведенной области памяти – памяти данных (Data Memory), расположенной внутри микросхемы сигнального процессора. Объем памяти данных ADSP-2189M составляет 48К 16-разрядных слов. Максимальное количество дискретных отсчетов АЦП, хранящихся во внутренней оперативной памяти данных процессора, не может превышать 49 152 (48х1024) точек. При выполнении программы элементы массива можно циклически читать одной ассемблерной командой

MХ0 = DM (I0,M1), где MX0 – регистр умножителя–накопителя, I0 и M1 – индексные регистры генератора адреса, которые хранят адрес ячейки памяти (I0) и – шаг изменения адреса (М1). Например, если перед первым выполнением команды DM в регистрах были записаны значения I0=5, М1=1, то после выполнения команды в регистр MХ0 процессор запишет 16-разрядное двоичное число пятой ячейки буфера данных (I0=5) и увеличит адрес на единицу (М1=1). При повторном проходе этой ветви программы выполнение команды

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.