хранения промежуточных вычислений и исходных данных.

5) ПЗУ для хранения программы выполняющую цифровую коррекцию.

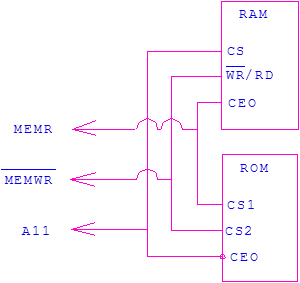

Для коммутации памяти ОЗУ или ПЗУ можно использовать выводы шины адреса А11, (при этом разрядность памяти нужно взять 2048´8) и нам достаточно одиннадцать выводов ША А0-А10. Если сигнал на ША А11=0 то мы работаем с ПЗУ, если А11=1 то с ОЗУ.

Подключение ПЗУ и ОЗУ к системному контроллеру и МП производится с помощью таблиц состояния (в этих таблицах указывается состояние микросхемы в зависимости от того на какие входы микросхемы и какого уровня сигналы подаются) соответствующих микросхем, с таким расчетом что если происходит обращение к одному устройству другое находится в третьем состоянии.

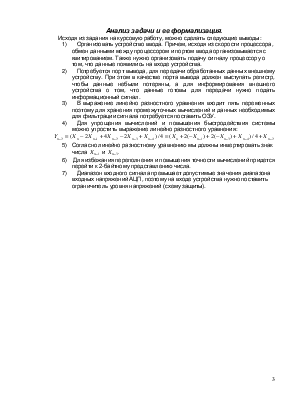

Для обращения к портам ввода и вывода, для уменьшения аппаратных затрат, можно использовать линии ША А12 – А13, объединенные с соответствующими сигнальными линиями системного контроллера с помощью логических элементов, во избежания неоднозначности при обращении к портам.

6) В качестве устройства ввода выступает АЦП К1108ПВ2А. При этом надо организовать обмен данными между процессором и АЦП.

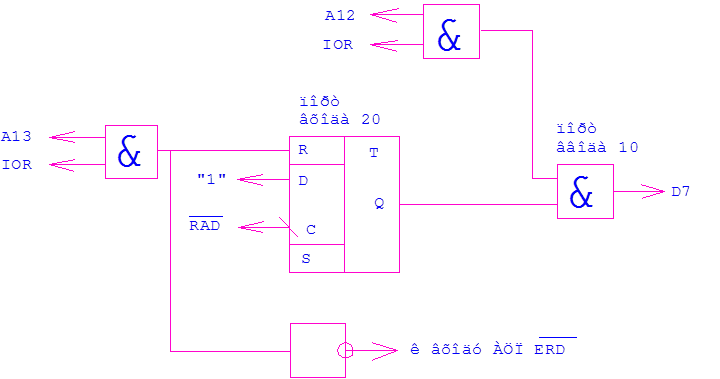

После преобразования аналогового сигнала в цифровой АЦП

подает сигнал ![]() . Чтобы процессор получил этот

сигнал, мы должны организовать схему хранения этого сигнала. В качестве этой

схемы выступает триггер. Триггер соединяем с отводом шины данных D7 через логический ключ. Ключ получает имя: «порт входа

10». Нужно организовать логическую схему обращения к этому порту, схему вывода

данных из порта в МКП и после этого сигнал, обнуляющий триггер. АЦП и триггер

получают названия: «порт входа 20».

. Чтобы процессор получил этот

сигнал, мы должны организовать схему хранения этого сигнала. В качестве этой

схемы выступает триггер. Триггер соединяем с отводом шины данных D7 через логический ключ. Ключ получает имя: «порт входа

10». Нужно организовать логическую схему обращения к этому порту, схему вывода

данных из порта в МКП и после этого сигнал, обнуляющий триггер. АЦП и триггер

получают названия: «порт входа 20».

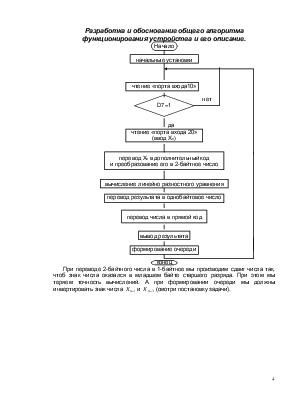

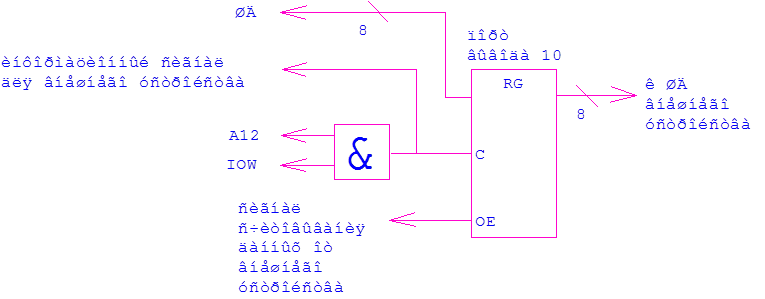

7) Для организации вывода данных во внешнее устройство потребуются: регистр, при этом для записи данных в регистр потребуется подать управляющий сигнал и номер порта вывода. Порт вывода называется: «порт вывода 10».

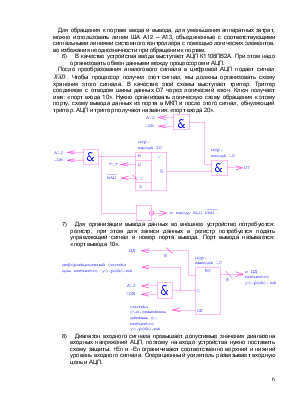

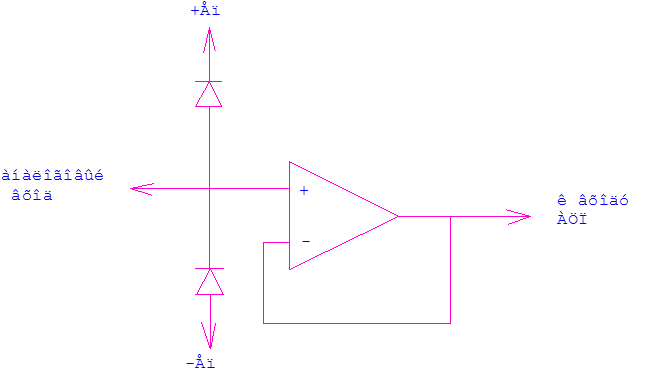

8) Диапазон входного сигнала превышает допустимые значения диапазона входных напряжений АЦП, поэтому на входе устройства нужно поставить схему защиты. +ЕП и -ЕП ограничивают соответственно верхний и нижний уровень входного сигнала. Операционный усилитель развязывает входную цепь и АЦП.

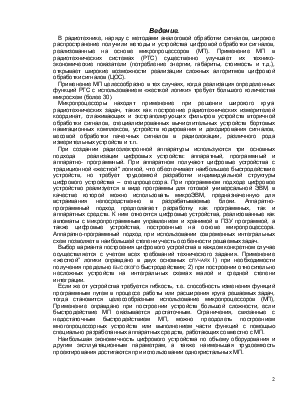

Синтез управляющего узла (разработка программы на языке микропроцессора).

; Курсовая работа

; на тему: Цифровой корректирующий фильтр

; выполнил: ст.гр. 913 Норотов А.В.

; Программа фильтрации сигнала.

;исходные данные

; линейное разностное уравнение У(n-2)=[X(n) - 2X(n-1) + 4X(n-2) - 2X(n-4)]/4 = [X(n) + 2[- X(n-1)] + 2[-X(n-4)]]/4 +

+ X(n-2)

; частота дискретизации Fд = 0.5 (кГц)

; входной сигнал – аналоговый, диапазон изменения (-3..+3)В

; аналого-цифровой преобразователь – К1108ПВ2

; выходной сигнал – 8-разрядныйпараллельный прямой код

; микропроцессор – КР580ВМ80А

;Программа на языке ассемблера.

SPACES ON

XN: .EQU 800H

XN_1: .EQU 802H

XN_2: .EQU 804H

XN_3: .EQU 806H

XN_4: .EQU 808H

P1: .EQU 80AH

P2: .EQU 80CH

S: .EQU 80EH

ADRSP: .EQU FFFH

PORTIN1: .EQU 10H

PORTIN2: .EQU 20H

PORTOUT: .EQU 10H

X: .DW 00H

Y: .DW 00H

Z: .DW 00H

;Подпрограмма начальных установок.

BGN: MACRO

LXI SP,ADRSP

IN PORTIN2

ENDM

;Подпрограмма ввода числа «X» из порта в аккумулятор и преобразование его в дополнительный код с последующим переводом в 2-байтное число. Результат записывается по адресу Х.

VVX: MACRO X

B1#: IN PORTIN1

RAL

JNC B1#

IN PORTIN2

РC_DC

1B_2B

SHLD X

ENDM

;Подпрограмма перевода числа в коде АЦП в дополнительный код.

РC_DC: MACRO

RAL

JNC C1#

CMA

RAR

ADI 1H

RAL

C1#: RAR

ENDM

;Подпрограмма перевода 1-байтного числа в 2-байтное.

1B_2B: MACRO

MOV L,A

RAL

MVI A,0H

SBI 0H

MOV H,A

ENDM

;Подпрограмма умножения числа находящегося по адресу X на 2-а. Результат умножения выводится по адресу Y.

MULTIP: MACRO X,Y

LHLD X

DAD H

SHLD Y

ENDM

;Подпрограмма суммирования 2-х чисел, находящихся по адресу X и Y. Результат выводится по адресу Z.

SUM: MACRO X,Y,Z

LHLD X

XCHG

LHLD Y

DAD D

SHLD Z

ENDM

;Деление на 4-е. Делимое находится в регистровой паре HL. Результат выводится по адресу X.

DELEN4: MACRO X

MOV A,H

RAR

MOV H,A

MOV A,L

RAR

MOV L,A

MOV A,H

RAR

MOV H,A

MOV A,L

RAR

MOV L,A

SHLD X

ENDM

;Перевод 2-х байтного числа в1-байтное. Исходные данные находятся в регистровой паре HL. Результат находится в аккумуляторе.

2B_1B: MACRO

MOV A,H

RAR

MOV H,A

MOV A,L

RAR

MOV L,A

MOV A,H

RAR

MOV H,A

MOV A,L

RAR

ENDM

;Перевод результата вычислений из дополнительного кода в прямой. Исходные данные и результат находятся в аккумуляторе.

DC_PC: MACRO

RAL

JNC D1#

RAR

SUI 1H

RAL

CMA

D1#: RAR

ENDM

;Вывод результата, находящегося в аккумуляторе, в порт.

OUTPUT: MACRO

OUT PORTOUT

ENDM

;Формирование очереди.

OCHARED: MACRO

LHLD XN_3

SHLD XN_4

ENVERT XN_2,XN_3

LHLD XN_1

SHLD XN_2

ENVERT XN,XN_1

ENDM

.CODE

;Подпрограмма изменения знака числа на противоположный.

ENVERT: MACRO X,Y

LDA X

DC_PC

ADI 80H

PC_DC

1B_2B

SHLD Y

ENDM

.CODE

;Основная программа.

ORG 06H

BGN

A1: VVX XN

MULTIP XN_1,P1

MULTIP XN_3,P2

SUM XN,XN_4,S

SUM S,P1,S

SUM S,P2,S

DELEN4 S

SUM S,XN_2,S

2B_1B

DC_PC

OUTPUT

OCHARED

JMP A1

.END

Оценка быстродействия устройства.

Программа

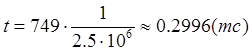

занимает 212 байт в ПЗУ. Максимальное время выполнения программы 749 машинных

тактов или  . Максимальное

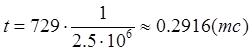

время выполнения основного цикла программы 729 машинных тактов или

. Максимальное

время выполнения основного цикла программы 729 машинных тактов или  . При этом время

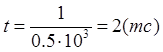

поступления данных в процессор

. При этом время

поступления данных в процессор  .

.

Составление принципиальной схемы устройства и ее описание.

1)

Для

осуществления синхронизации работы МП нужно к нему подключить генератор

тактовых импульсов КР580ГФ24. К нему должен подключаться кварцевый резонатор с

частотой ![]() (МГц).

(МГц).

2)

Схема

запуска МКП. Вход ![]() подключается к RC цепочке. Емкость должна заряжаться за 20..30 тактов

генератора. Параметры времязадающей цепи следующие:

подключается к RC цепочке. Емкость должна заряжаться за 20..30 тактов

генератора. Параметры времязадающей цепи следующие: ![]() (кОм),

(кОм), ![]() (мФ), диод

(мФ), диод ![]() .

.

3) Системный контроллер и шинный формирователь КР580ВК28 для фиксации слова состояния МП, выработки системных управляющих сигналов, буферизации шины данных и управления направлением передачи данных, а также на случай усовершенствования системы, путем введения дополнительных задач, решаемых процессором.

4) ОЗУ. Исходя из времени обращения к памяти, из малой нагрузочной способности (что позволяет не использовать шинный формирователь) выбираю микросхему КР537РУ10 с организацией 2048´8.

5) ПЗУ. Исходя из аналогичных требований, которые были предъявлены к ОЗУ, выбираю масочное ПЗУ на основе КМОП-структуры КА1603РЕ1 с организацией 2048´8.

6) В качестве устройства ввода выступает АЦП К1108ПВ2А. Для организации обмена данными между процессором и АЦП нам потребуются три инвертора (используем ИМС К561ЛН2, которая содержит шесть инверторов); три логических элемента «и» (используем ИМС К561ЛН2, которая содержит четыре элемента «и»); один «D» триггер (используем ИМС КР1564ЛИ1, которая содержит два триггера).

7) Для организации вывода данных во внешнее устройство потребуются:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.