СОДЕРЖАНИЕ

1.1. Схема К155ИП2П

1.2. Схема К155ЛН1

1.3. Схема К155ИП1П

1.4. Схема К555ТМ2 (D-триггер)

1.5. Схема К589АП26 (шинный формирователь с инверсией)

1.6. Схема К581ВА1 (параллельно-последовательный преобразователь)

ЗАКЛЮЧЕНИЕ

ПРИЛОЖЕНИЯ

Приложение 1: Текст программы, моделирующей работу схемы

Приложение 2: Результаты моделирования схемы

ЗАДАНИЕ

Необходимо описать работу схемы на языке VHDL :

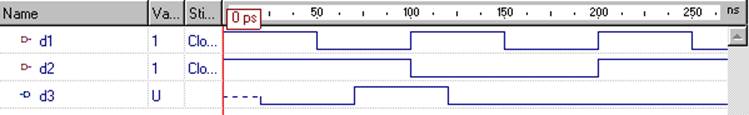

СХЕМА :

Введение.

Широкое распространение цифровой техники, ее доступность обывателю и дешевизна обусловлены появлением интегральных микросхем. Цифровые устройства, собранные на базе дискретных транзисторов и диодов, имели значительные габаритные размеры и массу; обладали невысокой надежностью в связи с наличием большого числа элементов и паяных связей между ними. Интегральные микросхемы, содержащие в своем составе десятки и сотни тысяч компонентов, позволили по-новому подойти к проектированию и изготовлению цифровых устройств. Надежность одной микросхемы практически не зависит от количества включенных в нее элементов и близка к надежности одиночного транзистора, а потребляемая мощность в пересчете на отдельный компонент уменьшается с ростом степени интеграции.

В процессе усовершенствования интегральных технологий стало возможным создание сложнейших устройств, надежных и обладающих малыми габаритами и высоким быстродействием.

1. МОДЕЛИРОВАНИЕ ЭЛЕМЕНТОВ

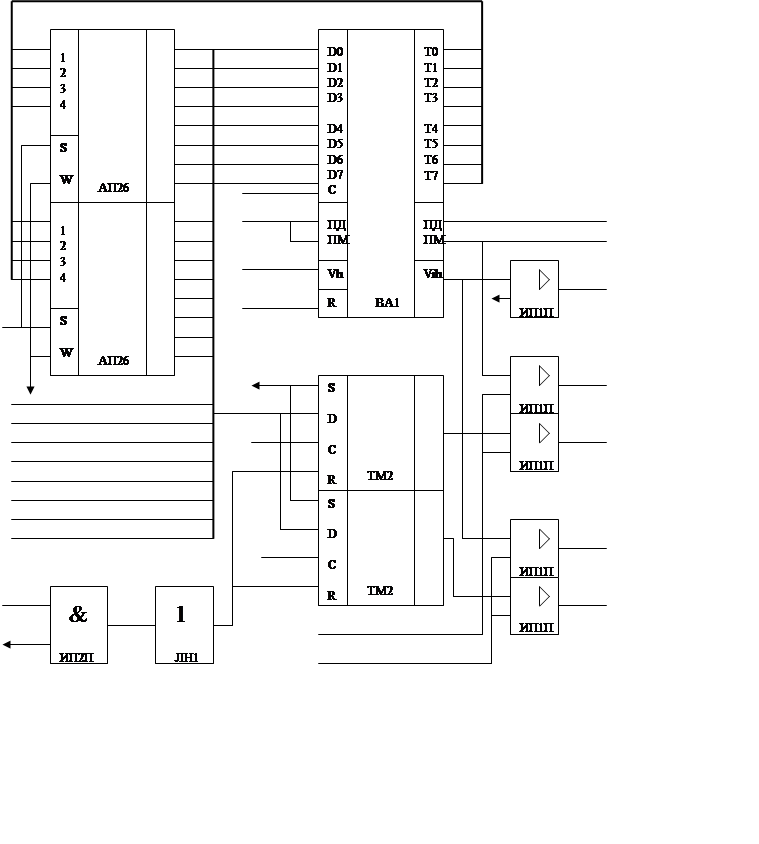

1.1. Схема К155ИП2П

|

||||

|

||||

![]() Данная схема реализует логическую функцию

Данная схема реализует логическую функцию

|

|

|

|

X2 |

Y |

|

|

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

0 |

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity ip2p is

port (

a01: in STD_LOGIC;

a02: in STD_LOGIC;

b03: out STD_LOGIC

);

end ip2p;

architecture ip2p of ip2p is

begin

process(a01,a02)

begin

b03<=not(a01) and not(a02) after 12 ns;

end process;

end ip2p;

|

Данная схема реализует логическую функцию

Y = not(X)

|

|

X |

Y |

||||

|

0 |

1 |

|||||

|

1 |

0 |

|||||

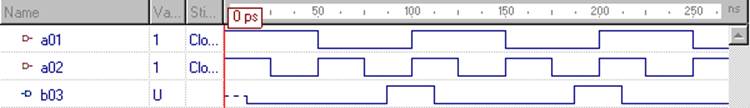

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity ln1 is

port (

a05: in STD_LOGIC;

b06: out STD_LOGIC

);

end ln1;

architecture ln1 of ln1 is

begin

process(a05)

begin

b06<=not(a05) after 18 ns;

end process;

end ln1;

|

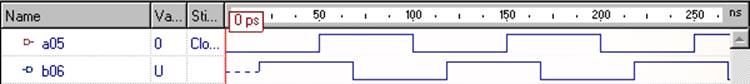

1.3.Схема К155ИП1П

Данная схема реализует логическую функцию

|

|

![]()

![]() Y = ‘0’ if X1 = ’0’

Y = ‘0’ if X1 = ’0’

![]()

|

|

|||

|

X |

X1 |

Y |

|

|

0 |

0 |

|

1 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

1 |

0 |

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity ip1p is

port (

d1: in STD_LOGIC;

d2: in STD_LOGIC;

d3: out STD_LOGIC

);

end ip1p;

architecture ip1p of ip1p is

begin

process(d1,d2)

begin

if d2='1' then d3<=not(d1) after 20 ns;

else d3<='0' after 20 ns;

end if;

end process;

end ip1p;

Временные диаграммы :

|

1.4.

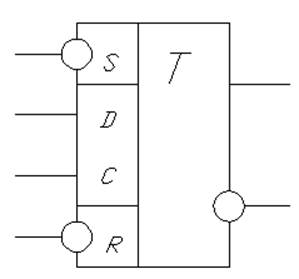

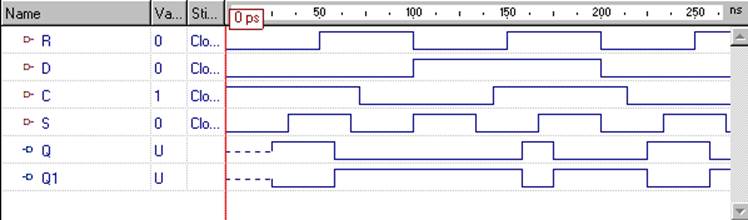

Схема К155ТМ2 (D-триггер)

1.4.

Схема К155ТМ2 (D-триггер)

- С – вход тактовых импульсов.

- D – вход установки триггера в состояние, в котором находится сигнал, поступающий на этот вход по спадам тактовых импульсов.

- R,S – управляющие входы (сигнал R устанавливает триггер в ‘1’, сигнал S – в ‘0’, если и R, и S равны ‘1’, то триггер устанавливается в ‘1’).

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity tm2 is

port (

R: in STD_LOGIC;

D: in STD_LOGIC;

C: in STD_LOGIC;

S: in STD_LOGIC;

Q: out STD_LOGIC;

Q1: out STD_LOGIC

);

end tm2;

architecture tm2 of tm2 is

begin

process (s,r,c,d)

variable q0,a: std_logic;

begin

a:='1';

if R='1'and S='0' and (C='1' or C='0')and (D='1' or D='0')then q0:='0';

else

if R='0' and S='1' and (C='1' or C='0')and (D='1' or D='0') then q0:='0';

else

If R='1' and S='1' then

if C'event and C='1' and D='1' then q0:='1';

else

if C'event and C='1' and D='0' then q0:='0';

end if;

end if;

else

if R='0' and S='0'and(C='1' or C='0')and (D='1' or D='0') then q0:=a;

end if;

end if;

end if;

end if;

q <= q0 after 25 ns;

a := q0;

q1<=not(q0) after 25 ns;

end process;

end tm2;

Временные диаграммы :

|

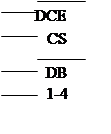

1.5 Схема K589AП26 ( шинный формирователь с инверсией)

Это микросхема представляет собой двунаправленный четырёхразрядный шинный формирователь, предназначенный для обмена данными между процессором и системной шиной.

В зависимости от управляющих сигналов DCE и CS микросхемы могут работать в режиме передачи DI®DВ, DВ®DO

![]()

![]()

|

|

![]()

![]()

|

![]()

|

|

|||||||

|

![]() library IEEE;

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity ap26 is

port (

cs: in STD_LOGIC;

dce: in STD_LOGIC;

DI: in STD_LOGIC_VECTOR (3 downto 0);

DB: inout STD_LOGIC_VECTOR (3 downto 0);

DO: out STD_LOGIC_VECTOR (3 downto 0)

);

end ap26;

architecture ap26 of ap26 is

begin

process(cs,dce,DI,DB)

begin

if (cs='0' and dce='0') then DB<=not(DI) after 16 ns;

end if;

if (cs='0' and dce='1') then DO<=not(DB) after 14 ns;

else DO<="0000" after 14 ns;

end if;

end process;

end ap26;

Временные диаграммы :

|

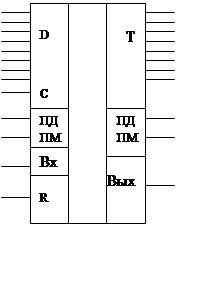

1.6. Схема КР581ВA1 (универсальный асинхронный приёмопередатчик)

Эта БИС предназначена для использования в мультиплексорах, концентраторах, печатоющих устройствах, индикаторах на ЭЛТ, а также в любых цифровых устройствах, где требуется преобразование параллельного кода в последовательный.

На ПД и ПМ подаются тактовые импульсы. При достижении 16 импульсов происходит инверсия выхода ''вх''. На выходе ''Т'' формируется параллельный код с входа ''D'' по заднему фронту ''С''. На выходе ''вых'' появляется последовательный код с ''Т'' опираясь на ''вх'' при переходе R с 0 в 1.

|

Текст программы :

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity va1 is

port (

D: in STD_LOGIC_VECTOR (7 downto 0);

c: in STD_LOGIC;

pd1: in STD_LOGIC;

pm1: in STD_LOGIC;

r: in STD_LOGIC;

vh: out STD_LOGIC;

T: inout STD_LOGIC_VECTOR (7 downto 0);

pd2: out STD_LOGIC;

pm2: out STD_LOGIC;

vih: out STD_LOGIC

);

end va1;

architecture va1 of va1 is

signal

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.