Федеральное агентство образования Российской Федерации

Рязанский государственный радиотехнический университет

Кафедра САПР ВС

Пояснительная записка к курсовому проекту по курсу

Выполнил:

студент гр. 445

Проверил:

доцент каф. САПР ВС

Содержание

1.Введение……………………………………………………………………………...3

2.Описание схемы……………………………………………………………………...4

3.Описание элементов схемы………………………………………………………….5

3.1.Микросхема К133ЛП5……………………………………………………………..5

3.2.Микросхема К133ИР13…………………………………………………………….7

3.3.Микросхема К133ИЕ5…………………………………………………………….10

3.4.Микросхема К585АП16…………………………………………………………..13

4.Моделирующая программа…………………………………………………………15

5.Заключение…………………………………………………………………………..21

Список литературы……………………………………………………………………22

1.Введение

Цифровая электроника плотно вошла в жизнь современного человека, мы каждый день встречаемся с ней в повседневности. Цифровые микросхемы совершенствуются, уменьшаясь при этом в размерах и получая возможность осуществлять все более разнообразные функции. В данной работе моделируется цифровая схема. Ёе изучение производится с помощью языка VHDL который позволяет решать задачи верификации и синтеза схем с различной степенью детальности их описания и, таким образом, объединять этапы проектирования в единый процесс нисходящего проектирования "сверху вниз". Появление языка VHDL в определенной степени позволяет автоматизировать задачи проектирования от описания алгоритма функционирования ДС до реализации кристаллов микросхем.

2.Описание схемы

Данная схема представляет собой часть сигнатурного анализатора.

Формирователь тестовых воздействий позволяет получить 16-разрядный двоичный (ДК) и псевдослучайный (ПСК) коды на своих выходах. Сигналы с выходов подаются на входы исследуемой схемы. Также с формирователя ДК на узел управления подается сигнал, определяющий окончание одного цикла измерения. ДК формируется с помощью двоичных счетчиков DD14…DD17, а ПСК – с помощью схемы на сдвиговых регистрах с обратными связями DD18, DD19, DD28. С выходов счетчиков и регистров сигналы ДК и ПСК подаются на буферные элементы DD20…DD27, обеспечивающие повышенную нагрузочную способность формирователей. Это позволяет подключить к их выходам до 30 стандартных ТТЛ-входов.

3.Описание элементов схемы.

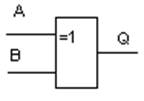

3.1 Элемент К133ЛП5

Это элемент исключающее ИЛИ применяется как сумматор по модулю 2 или используется для задерживания цифрового импульса. Его часто включают как фазовый компаратор, определяющий момент равенства частот и фаз двух цифровых последовательностей.

Выходной сигнал элемента соответствует уравнению: Q=A+B=![]() где

где ![]() -суммирование по модулю 2.

-суммирование по модулю 2.

К133ЛП5

Таблица состояния рис1.

|

Вход |

выход |

|

|

А |

В |

Q |

|

H |

H |

H |

|

H |

B |

B |

|

B |

H |

B |

|

B |

B |

H |

![]()

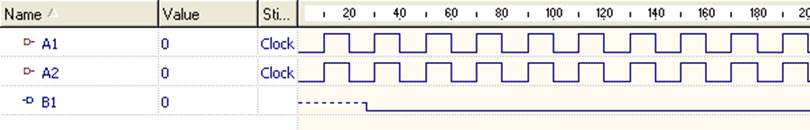

Текст моделирующей программы.

library IEEE;

use IEEE.std_logic_1164.all;

entity summator is

port (

A1: in STD_LOGIC;

A2: in STD_LOGIC;

B1: out STD_LOGIC

);

end summator;

architecture summator of summator is

begin

process(A1,A2)is

begin

B1<= transport A1 xor A2 after 27 nS;

end process;

end summator;

Работа элемента:

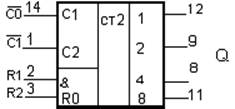

3.2 Элемент К133ИЕ5

Четырехразрядный, асинхронный счетчик пульсаций, имеет две части : делитель на 2 и делитель на восемь. В данной схеме применяется как счетчик- делитель на 16 т.к. вывод 12 соединен с выводом 1, логические уровни будут соответствовать таб.2 и таб.3:

К133ИЕ5

Таблица 2.Последовательность счета.

|

счет |

выход |

счет |

выход |

||||||

|

Q0 |

Q1 |

Q2 |

Q3 |

Q0 |

Q1 |

Q2 |

Q3 |

||

|

0 |

Н |

Н |

Н |

Н |

8 |

Н |

Н |

Н |

В |

|

1 |

В |

Н |

Н |

Н |

9 |

В |

Н |

Н |

В |

|

2 |

Н |

В |

Н |

Н |

10 |

Н |

В |

Н |

В |

|

3 |

В |

В |

Н |

Н |

11 |

В |

В |

Н |

В |

|

4 |

Н |

Н |

В |

Н |

12 |

Н |

Н |

В |

В |

|

5 |

В |

Н |

В |

Н |

13 |

В |

Н |

В |

В |

|

6 |

Н |

В |

В |

Н |

14 |

Н |

В |

В |

В |

|

7 |

В |

В |

В |

Н |

15 |

В |

В |

В |

В |

Таблица 3.Режим работы счетчика.

|

Вход сброса |

Выход |

||||

|

R1 |

R2 |

Q0 |

Q1 |

Q2 |

Q3 |

|

B |

B |

H |

H |

H |

H |

|

H |

B |

Счет |

|||

|

B |

H |

» |

|||

|

H |

H |

» |

|||

Текстмоделирующейпрограммы.

File: K133ie5.vhd

-- created by Design Wizard: 04/15/07 10:15:27

-library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity K133ie5 is

port (

C2: in STD_LOGIC;

R1: in STD_LOGIC;

R2: in STD_LOGIC;

Q: out STD_LOGIC_VECTOR (3 downto 0)

);

end K133ie5;

architecture K133ie5 of K133ie5 is

begin

process (C2,R1,R2)

variable D: STD_LOGIC_VECTOR (3 downto 0):= "0000";

begin

if R1='1'and R2='1' then

Q<= transport "0000" after 26 ns;

elsif C2='0' and C2’DELAYED=’1’ and D<15 then

D:=D+1;

end if;

Q<=transport D after 26 ns;

end process;

-- <<enter your statements here>>

end K133ie5;

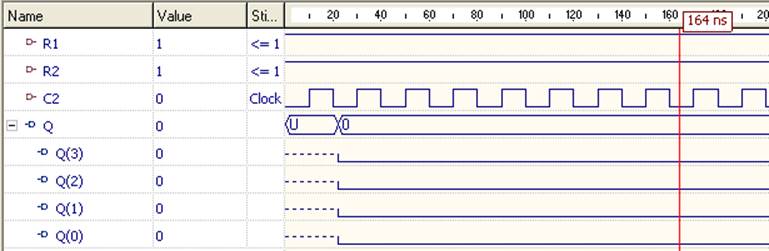

сброс счетчика:

Режим счета:

3.3 Элемент К133ИР13

Это универсальный, восьмиразрядный, синхронный регистр сдвига. Каждая операция продолжается в регистре не более 20нс, поэтому он пригоден для обслуживания скоростных процессоров и ЗУ как буферный накопитель байта. Синхронную работу регистру обеспечивают специальные входы выбора режима (S0 и S1 напряжения низкого уровня), параллельной загрузки (на этих входах напряжения высокого уровня), сдвига влево( S1-в S0-н) и сдвига вправо( S1-н S0-в).Кроме однотипных параллельных входов D0-D7,первый и последний разряды регистра имеют дополнительные D- входы: DSR- для сдвига вправо и DSL- для сдвига влево. Состоянием входов S0 и S1 определяется также прием тактового перепада от входа C. В данной схеме осуществляет сдвиг вправо согласно таб.4.:

К133ИР13

Таблица 4. Состояние регистра.

|

Режим работы |

вход |

выход |

||||||||

|

С |

|

S1 |

S2 |

DSR |

DSL |

Dn |

Q0 |

Q1-Q6 |

Q7 |

|

|

сброс |

x |

H |

x |

x |

x |

x |

x |

H |

H-H |

H |

|

хранение |

|

B |

H |

H |

X |

X |

X |

q0 |

q1-q6 |

q7 |

|

Сдвиг влево |

|

B |

B |

H |

X |

H |

X |

q1 |

q2-q7 |

H |

|

|

B |

B |

H |

X |

B |

X |

q1 |

q2-q7 |

B |

|

|

Сдвиг вправо |

|

B |

H |

B |

H |

X |

X |

H |

q0-q5 |

q6 |

|

|

B |

H |

B |

B |

X |

X |

B |

q0-q5 |

q6 |

|

|

Параллельная нагрузка |

|

B |

B |

B |

B |

X |

dn |

d0 |

d1-d6 |

d7 |

Текст моделирующей программы

File: c:\my designs\K133ir13\SRC\K133ir13.VHD

-- created by Design Wizard: 04/15/07 11:22:19

-library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity K133ir13 is

port (

C: in STD_LOGIC;

DR: in STD_LOGIC;

S1: in STD_LOGIC;

S0: in STD_LOGIC;

R: in STD_LOGIC;

Y: out STD_LOGIC_VECTOR (7 downto 0)

);

end K133ir13;

architecture K133ir13 of K133ir13 is

begin

process(C,DR,S1,S0,R)is

variable sdvvl1: STD_LOGIC_VECTOR (6 downto 0);

variable sdvvl2: STD_LOGIC_VECTOR (7 downto 0);

begin

--obnulenie schetchika

if R='0' then

sdvvl2:="00000000";

--sdvig vpravo

elsif S1='0' and S0='1' then

if C='1' and C'DELAYED='0' and DR='0' then

sdvvl1(6 downto 0):=sdvvl2(6 downto 0);

sdvvl2(7 downto 1):=sdvvl1(6 downto 0);

sdvvl2(0):='0';

elsif C='1' and C'DELAYED='0' and DR='1' then

sdvvl1(6 downto 0):=sdvvl2(6 downto 0);

sdvvl2(7 downto 1):=sdvvl1(6 downto 0);

sdvvl2(0):='1';

end if;

end if;

Y<=transport sdvvl2 after 20 ns;

end process;

end K133ir13;

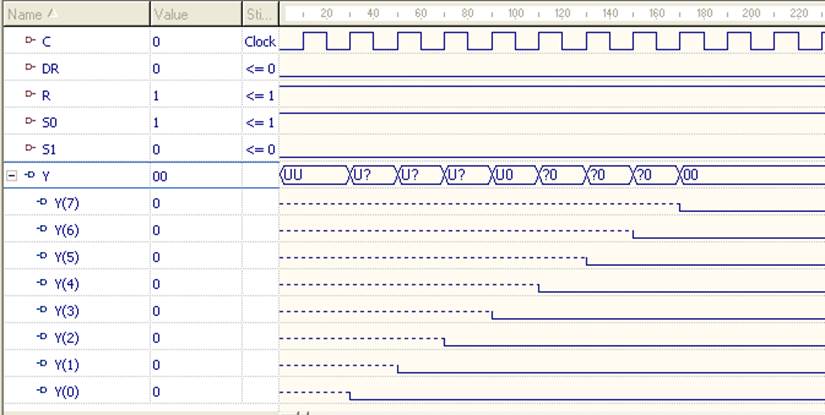

Режим работы:

сдвиг нуля:

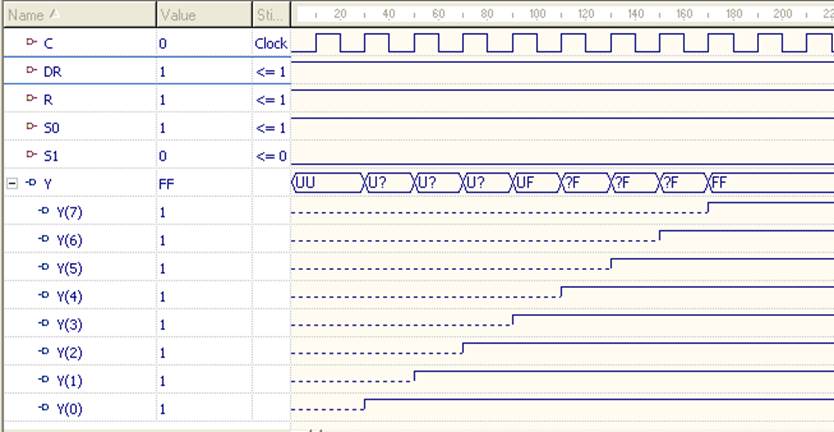

сдвиг единицы:

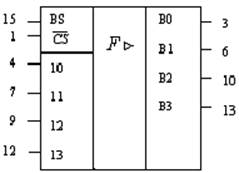

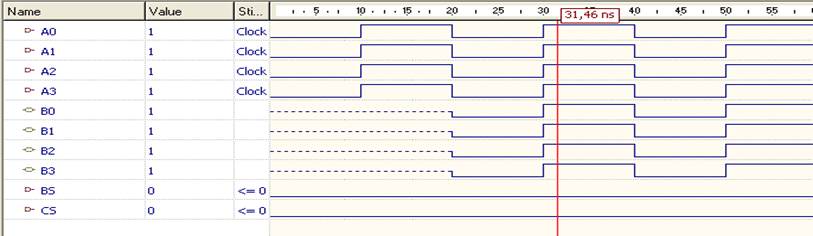

3.4.Элемент К585АП16

Шинный формирователь который является параллельным двунаправленным формирователем сигналов для управления магистралями ( шинами) в цифровых вычислительных устройствах. Представляет собой 4- канальный коммутатор , имеющий в каждом канале одну шину для приема информации, одну шину для выдачи и одну двунаправленную шину для приема и выдачи. Информация проходит без изменения таб.5:

К585АП16

Таблица 5.Логика передачи информации:

|

BS |

|

Направление передачи информации |

Выходы в выключенном состоянии |

|

0 |

0 |

От входа А на выход В |

С |

|

0 |

1 |

От входа В на выход С |

-------- |

|

1 |

1 |

Передача отсутствует |

С, В |

Текст моделирующей программы

File: K585ap16.vhd

-- created by Design Wizard: 04/15/07 13:39:22

-library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity K585ap16 is

port (

BS: in STD_LOGIC;

CS: in STD_LOGIC;

A0: in STD_LOGIC;

A1: in STD_LOGIC;

A2: in STD_LOGIC;

A3: in STD_LOGIC;

B0: inout STD_LOGIC;

B1: inout STD_LOGIC;

B2: inout STD_LOGIC;

B3: inout STD_LOGIC

);

end K585ap16;

architecture K585ap16 of K585ap16 is

begin

process(BS,CS,A0,A1,A2,A3)is

begin

if BS='0' and CS='0' then

B0<=transport A0 after 25ns;

B1<=transport A1 after 25ns;

B2<=transport A2 after 25ns;

B3<=transport A3 after 25ns;

end if;

end process;

end K585ap16;

режим работы:

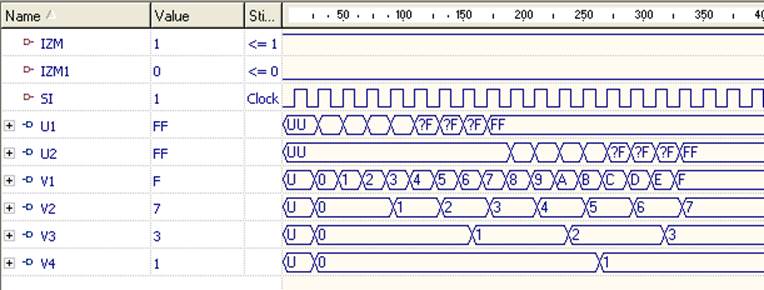

4.Моделирование схемы.

Для моделирования общей схемы представим её в следующем виде:

Текст моделирующей программы общей схемы.

library IEEE;

use IEEE.std_logic_1164.all;

entity vnsignal is

port (

IZM1: in STD_LOGIC;

IZM: in STD_LOGIC;

SI:in STD_LOGIC;

V1: out STD_LOGIC_VECTOR (3 downto 0);

V2: out STD_LOGIC_VECTOR (3 downto 0);

V3: out STD_LOGIC_VECTOR (3 downto 0);

V4: out STD_LOGIC_VECTOR (3 downto 0);

U1: out STD_LOGIC_VECTOR (7 downto 0);

U2: out STD_LOGIC_VECTOR (7 downto 0);

stop: out STD_LOGIC);

end vnsignal;

architecture vnsignal of vnsignal is

component K133ir13 is

port (

C: in STD_LOGIC;

DR: in STD_LOGIC;

S1: in STD_LOGIC;

S0: in STD_LOGIC;

R: in STD_LOGIC;

Y: out STD_LOGIC_VECTOR (7 downto 0));

end component;

component K133ie5 is

port (

C2: in STD_LOGIC;

R1: in STD_LOGIC;

R2: in STD_LOGIC;

Q: out STD_LOGIC_VECTOR (3 downto 0));

end component;

component summator is

port(

A1: in STD_LOGIC;

A2: in STD_LOGIC;

B1: out STD_LOGIC );

end component;

--signali s schetchika

signal V14,V15,V16,V17:STD_LOGIC_VECTOR (3 downto 0):="0000";

--signali s registra

signal U18,U19:STD_LOGIC_VECTOR (7 downto 0);

--signali s ili

signal I11, I12 ,I13:STD_LOGIC;

signal I14:STD_LOGIC:='1';

--zemlia

signal Z:STD_LOGIC:='0';

--pitanie

signal pitanie: STD_LOGIC:='1';

begin

DD14:K133ie5

port map (

C2=>SI,

R1=>IZM1,

R2=>IZM1,

Q=>V14);

DD15:K133ie5

port map (

C2=>V14(0),

R1=>IZM1,

R2=>IZM1,

Q=>V15);

DD16:K133ie5

port map (

C2=>V15(0),

R1=>IZM1,

R2=>IZM1,

Q=>V16);

DD17:K133ie5

port map (

C2=>V16(0),

R1=>IZM1,

R2=>IZM1,

Q=>V17);

DD18:K133ir13

port map(

C=>SI,

DR=>’1’,

S1=>Z,

S0=>pitanie,

R=>IZM,

Y=>U18);

DD19:K133ir13

port map(

C=>SI,

DR=>U18(7),

S1=>Z,

S0=>pitanie,

R=>IZM,

Y=>U19);

DD28_1:summator port map(

A1=>U18(6),

A2=>U19(0),

B1=>I11);

DD28_2:summator port map(

A1=>U18(3),

A2=>U19(7),

B1=>I12);

DD28_3:summator port map(

A1=>I11,

A2=>I12,

B1=>I13);

DD28_4:summator port map(

A1=>I13,

A2=>pitanie,

B1=>’1’);

V1<=V14;

V2<=V15;

V3<=V16;

V4<=V17;

U1<=U18;

U2<=U19;

stop<=V17(0);

end vnsignal;

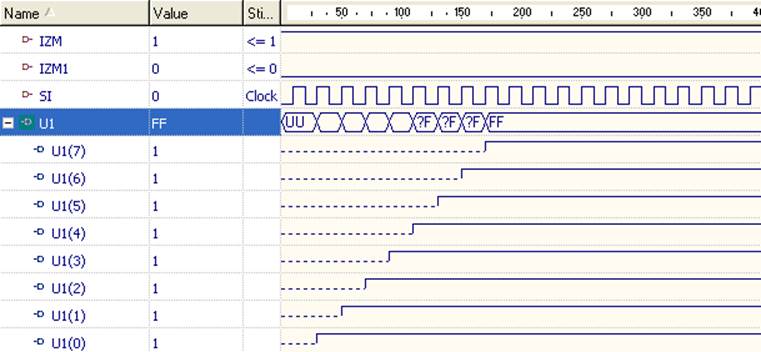

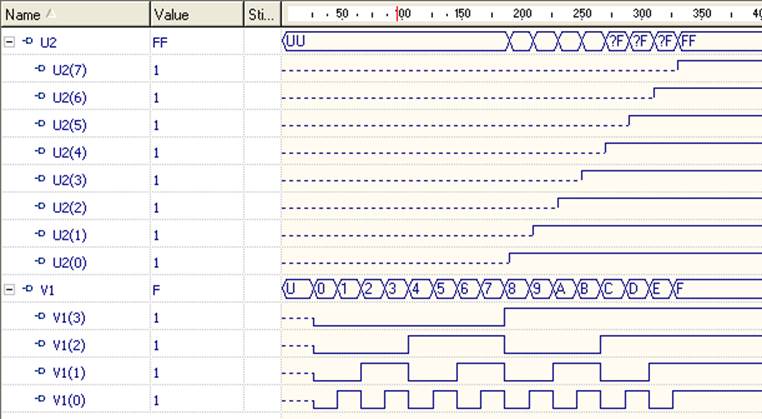

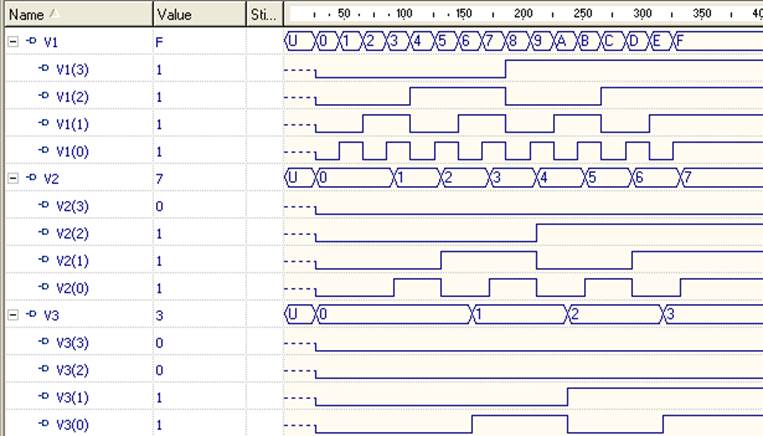

Рис. 11. Вейвформы моделируемой схемы:

5.Заключение

С помощью данной курсовой работы был частично освоен язык VHDL и принципы моделирования схемы с помощью него. Также произошло ознакомление с некоторыми базовыми элементами ТТЛ-логики.

Список литературы.

1. «Active-VHDL On-line Documentation» - электронное пособие.

2. Шило В. Л. «Популярные цифровые микросхемы», справочник, 2-е изд. Челябинск, «Металлургия», 1989 г.

3. «Микропроцессорные средства и системы» №2, 1988 г.

4. С.В. Якубовский «Аналоговые и цифровые интегральные микросхемы»

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.