По способу формирования следующего адресса микрокоманды

Используют две системы адресации.

1) Принудительная

2) Естественная.

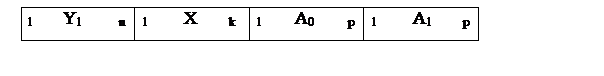

Операционная часть Адресная часть

|

X – номер логического условия

А0 – адрес перехода при единичном значении логического условия.

А1 – адрес перехода при нулевом значении логического условия.

|

|||

|

|||

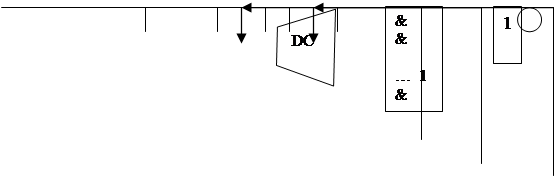

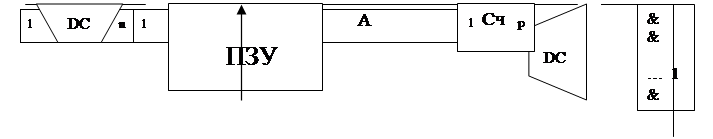

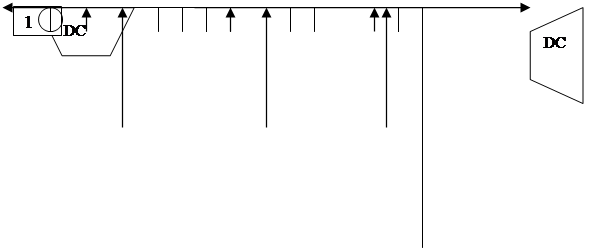

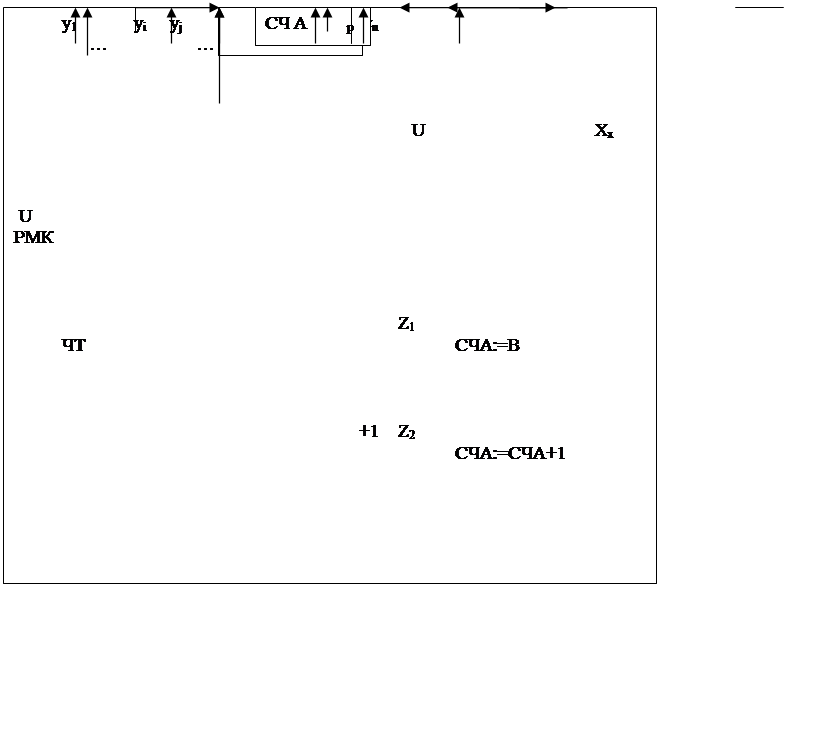

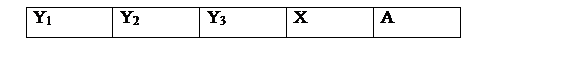

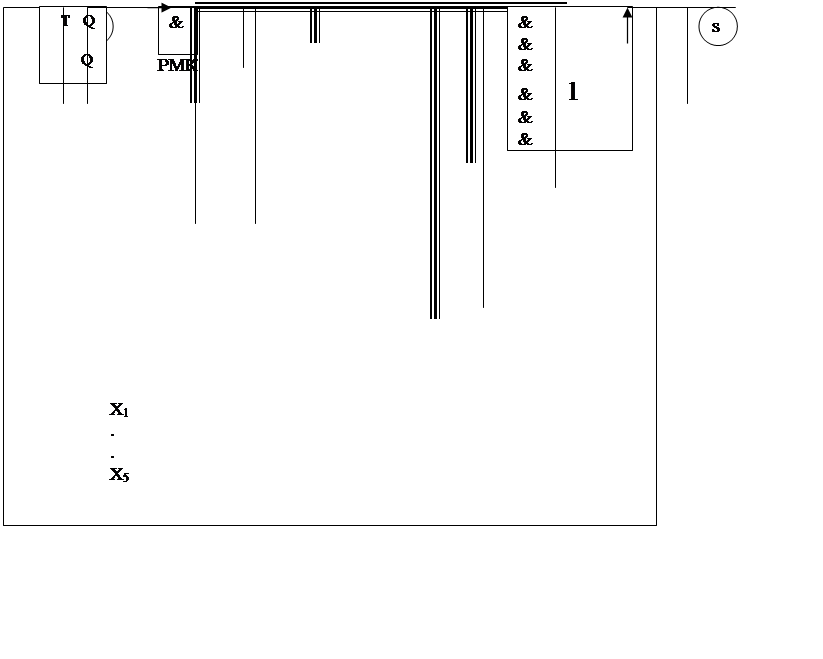

В исходном состоянии управляющий триггер

находится в «0»

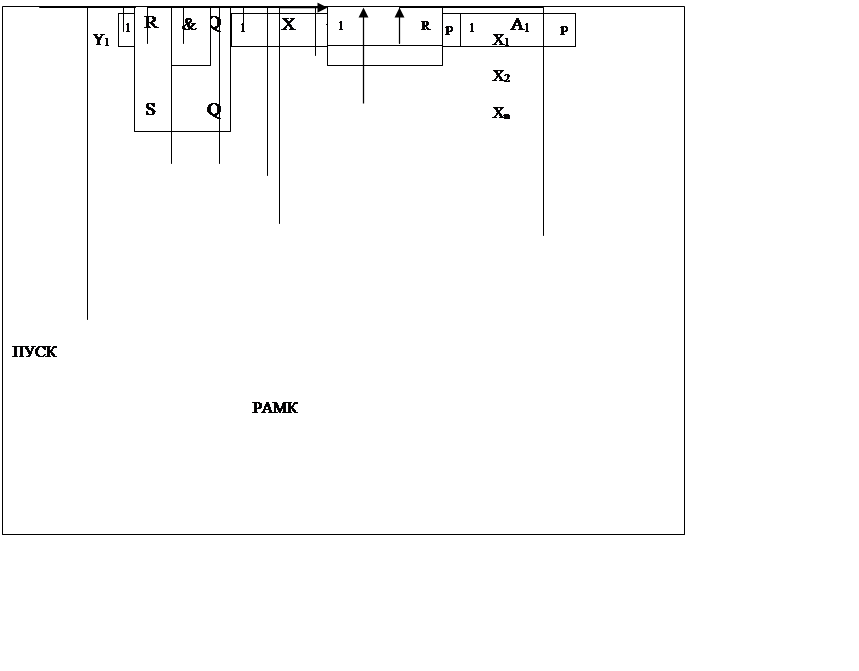

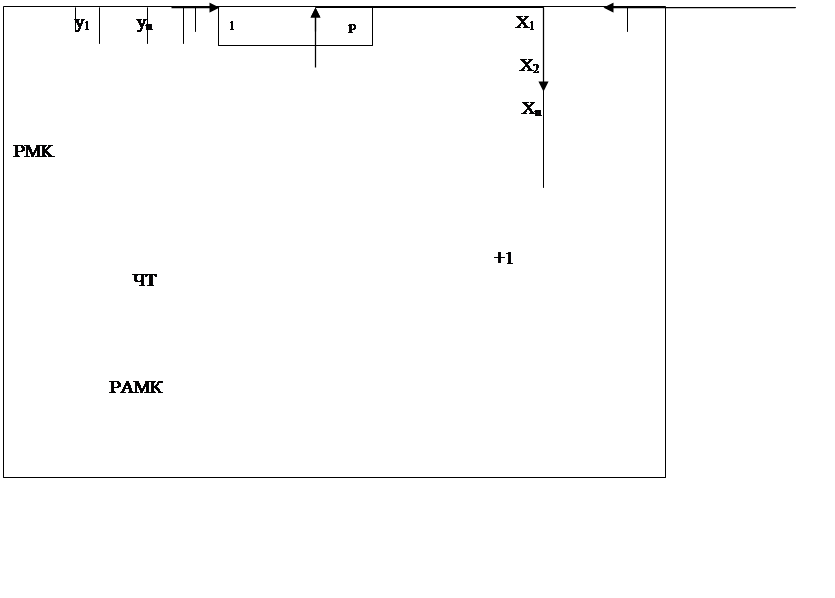

После включения включается автоматическое обнуление регистра адреса МК (РАМК), поэтому начальный адрес равен 0.

После нажатия кнопки «Пуск», управляющий триггер переходит в единичное состояние, разрешая прохождение синхроимпульса на схему управления ПЗУ.

По первому управляющему синхросигналу из ПЗУ считывается МК по адресу 0, затем осуществляется анализ каждого из 4 полей МК.

Выходное поле Х хранящее номер логического условия дешифрируется, возбуждая выходную шину соответствующего номера заданного условия. Если для выбранного условия его значение равно 1, то выходной сигнал с выхода схемы И – ИЛИ будет равен 1, что обеспечит передачу в регистр РАМК адреса А0 иначе передаётся А1 работа завершится при поступлении на вход R единичного сигнала.

|

|||

|

|

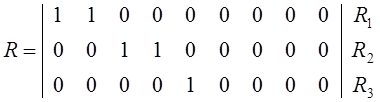

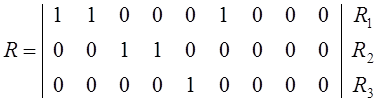

Принудительная.

Если МК содержит незначительное количество переходов использовать принудительную адресацию невыгодно т.к. каждая МК должна содержать практически неиспользуемое поле Х.

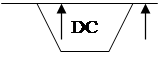

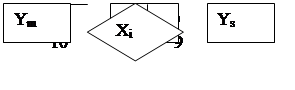

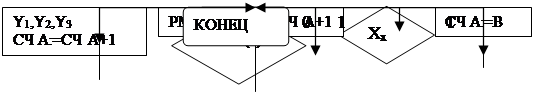

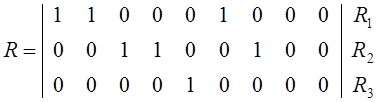

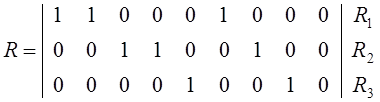

Для более экономичного использования ПЗУ используют естественную адресацию МК, при этом используют два типа микрокоманд

![]()

![]()

![]()

![]() ОПЕРАЦИОННЫЕ

ОПЕРАЦИОННЫЕ

![]()

![]()

УПРАВЛЯЮЩИЕ

УПРАВЛЯЮЩИЕ

![]()

![]()

![]()

![]()

|

|

|

|||

|

|

|

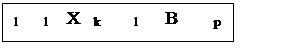

Затем анализируется 0 разряд МК, если это операционная МК, то происходит увеличение счётчика на 1 и выполняется заданный набор МК, если это управляющая МК то осуществляют анализ условия, номер которого хранится в поле Х, если 0, то только увеличивают счётчик на 1, иначе в счётчик адреса из адресного поля МК (В) загружается значение адреса МК.

Синтез УА с программируемой логикой.

Синтез сводится к программированию ПЗУ.

Пример:

|

|

|||||

|

|

||||

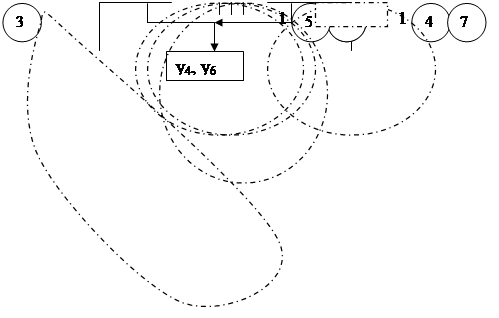

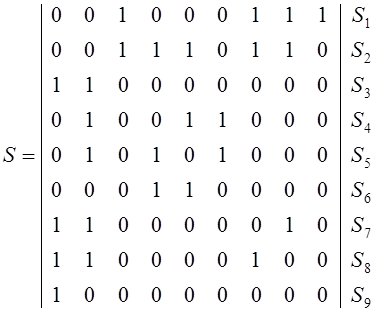

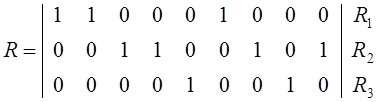

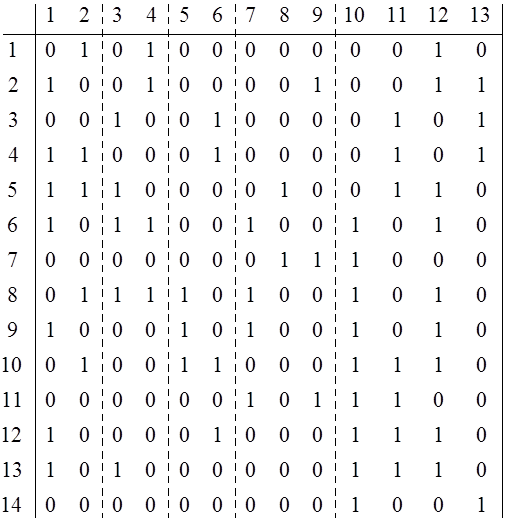

Осуществляем разбиение МК по полям операционной части МК таким образом, чтобы внутри каждого поля они были несовместимы между собой. Разбиение осуществляется на основе матриц включения и матриц совмстимости.

Матрица совместимости:

1) ![]()

![]()

2) ![]()

![]()

3) ![]()

![]()

4) ![]()

![]()

5) ![]()

![]()

![]()

6) ![]()

7) ![]()

![]()

8) ![]()

![]()

![]()

9) ![]()

![]()

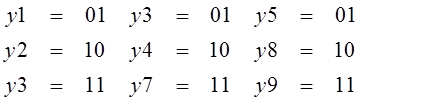

Y1={y1, y2, y6}; Y2={y3, y4, y7, y9}; Y3={y5, y8};

или

Y1={y1, y2, y6}; Y2={y3, y4, y7 }; Y3={y5, y8, y9};

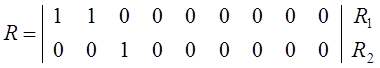

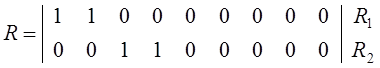

|

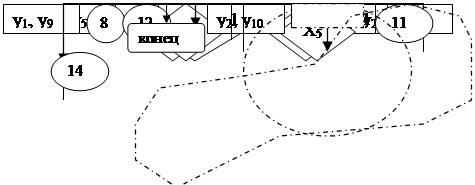

x1: 001

x2: 000

x3: 011

x4: 110

x5: 101

одна МК 13 бит, команд 14 штук. 13*14=182 бита.

|

|

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.