|

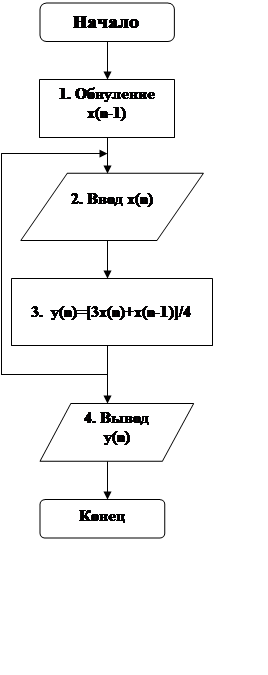

В блоке 1 происходит первоначальное обнуление х(n-1), что необходимо для обработки первых входных данных.

В блоке 2 происходит считывание входных данных и преобразование их в форму доступную для обработки в МП.

В блоке 3 происходит вычисление линейно разностного уравнения y(n)=[3x(n)+x(n-1)]/4 и запоминание в регистре значения х(n) для использования как х(n-1) в вычислении следующего значения y(n).

В блоке 4 происходит преобразование в нужный код и вывод значения y(n) в запоминающий регистр.

Структурная схема вычислительного устройства представлена на рисунке.

|

Разрабатываемое устройство должно содержать следующие узлы: микропроцессор, тактовый генератор, ПЗУ, системный контроллер, АЦП и выходной порт.

В качестве микропроцессора будем использовать микросхему КР580ВМ80. Микропроцессор тактируется генератором КР580ГФ24, который вырабатывает тактовые импульсы, импульс сброса и обеспечивает синхронизацию всего устройства в целом. Так как КР580ВМ80 имеет довольно слабые сервисные возможности, непосредственно с ним сопрягается системный контроллер КР580ВК28, который обеспечивает работу с памятью и портами, а так же аппаратно формирует команду векторного прерывания RST7. Для хранения программы используется ПЗУ КР556РТ17 емкостью 512 байт. ПЗУ большего объема использовать не имеет смысла, так как и этого объема вполне достаточно. Использование ОЗУ в данном устройстве нецелесообразно, поскольку для хранения одного отсчета можно обойтись регистрами микропроцессора. В качестве АЦП будем использовать микросхему из технического задания К1108ПВ1. В качестве выходного порта необходимо использовать устройство хранения информации емкостью 1 байт. Для нашей цели подойдет регистр хранения К555ИР22. В силу того, что используемый АЦП в цифровом фильтре работает при определенных входных напряжениях (0…2,5В) его необходимо согласовать с напряжением заданным в техническом задании (-4…+4В) для чего необходимо использовать быстродействующий операционный усилитель. В нашем случае будем использовать ОУ К140УД7, так как он имеет выводы балансировки смещения нуля.

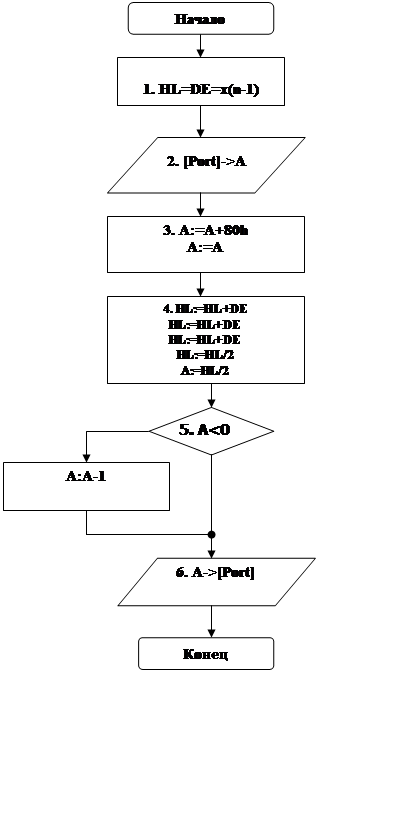

Входным сигналом является аналоговый сигнал, который преобразуется АЦП в параллельный код, этот код нужно скорректировать, т.к. МП работает в параллельном дополнительном коде. Макрос Read_Port осуществляет: чтение входных данных из АЦП в регистр DE, а так же преобразование кода АЦП в дополнительный код с которым может работать МП. Макрос Write_Port осуществляет: вывод результата в порт в обратном коде.

Операцию умножения на три и сложение с предыдущим отчетом можно заменить операциями сложения, а деление на 4 путем деления на два, дважды:

y(n)={[x(n)+x(n-1)]+[ x(n)+x(n-1)]+[ x(n)+x(n-1)]}/2/2

Так как в моем случае переполнения на выходе возникать не могут, то программа не использует специальных средств устраняющих это явление. С переполнением в вычислениях помогает то, что используются двух байтные регистровые пары HL и DE. Макрос DEVIDE осуществляет деление на два. Но так как в уравнении производится деление на четыре, к данному макросу придется обратиться дважды.

По адресу 0 в ПЗУ располагается короткая программа инициализации. Ее задача состоит в том, чтобы установить начальное значение x(n-1):=0.

В данном устройстве для промежуточных вычислений удается обойтись только регистрами микропроцессора, поэтому ОЗУ не используется, а для хранения х(n-1) используется регистр HL.

В программе имеются холостые команды, которые служат для выравнивания тактов в ходе ветвления, это позволяет выводить информацию одновременно.

Ниже приводится алгоритм работы управляющей программы:

|

Составление принципиальной схемы устройства и ее описание

На входы F1 и F2 микропроцессора КР580ВМ80А подаются две противофазные последовательности тактовых импульсов с частотой 2 МГц от генератора КР58ГФ24. При нажатии кнопки SB1 на входе процессора Reset появляется импульс, сбрасывающий программный счетчик, и запускается программа инициализации. Работа генератора и микропроцессора синхронизируется через выходы Sync.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.