Микросхемы состоят из набора повторителей или инверторов, объединенных общим управлением. Структура ШФ допускает параллельное использование нескольких таких микросхем. Выбирают ту или иную микросхему, т. е. переводят ее в активное состояние сигналом на вход выбора кристалла ВК. Установка на входе ВК «О» обеспечивает возможность управления выдачей информации по входу УВ.

Данные могут поступать в микросхему по магистралям А

или В, а выдаваться — по магистралям В или С Если на входе УВ установлена «1»,

то информация со входов В1-В4 «поступает»

на выходы C1—C4, в противном случае

информация со входов A1—A4 «поступает» на B1—В4.

Данные могут поступать в микросхему по магистралям А

или В, а выдаваться — по магистралям В или С Если на входе УВ установлена «1»,

то информация со входов В1-В4 «поступает»

на выходы C1—C4, в противном случае

информация со входов A1—A4 «поступает» на B1—В4.

Микросхема К589АП26 отличается oт микросхемы К589АП16 тем, что входная информация, проходя через инверторы, изменяет свое значение на инверсное.

Рисунок 2.33 Условное

обозначение К589АП26

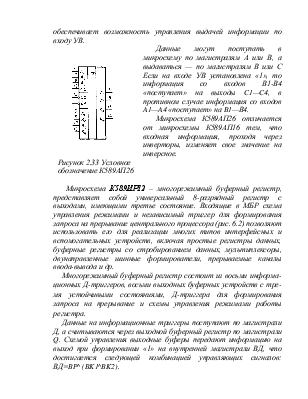

Микросхема К589ИР12 – многорежимный буферный регистр,представляет собой универсальный 8-разрядный регистр с выходами, имеющими третье состояние. Входящие в МБР схема управления режимами и независимый триггер для формирования запроса на прерывание центрального процессора (рис. 6.2) позволяют использовать его для реализации многих типов интерфейсных и вспомогательных устройств, включая простые регистры данных, буферные регистры со стробированием данных, мультиплексоры, двунаправленные шинные формирователи, прерываемые каналы ввода-вывода и др.

Многорежимный буферный регистр состоит из восьми информационных Д-триггеров, восьми выходных буферных устройств с тремя устойчивыми состояниями, Д-триггера для формирования запроса на прерывание и схемы управления режимами работы регистра.

Данные на информационные триггеры поступают по магистрали Д, а считываются через выходной буферный регистр по магистрали Q. Схемой управления выходные буферы передают информацию на выход при формировании «1» на внутренней магистрали ВД, что достигается следующей комбинацией управляющих сигналов: ВД=BP^ (BK1^BK2).

При ВД=0 выходы схемы находятся в третьем состоянии. Устройство управления МБР позволяет записывать информацию с выходными каскадами, находящимися в третьем состоянии и повторяющими кодами входной магистрали. Режим записи информации соответствует уровню «I» на внутренней управляющей магистрали:

ЗП=(С^ВР)V(ВК1^ВК2^ВР).

В

случае, если режим записи обеспечивается сигналами С^ВР, выходные каскады

находятся в третьем состоянии, при организации записи сигналами BK1^ВК2^ВР информация входной магистрали подается на выходную магистраль.

В

случае, если режим записи обеспечивается сигналами С^ВР, выходные каскады

находятся в третьем состоянии, при организации записи сигналами BK1^ВК2^ВР информация входной магистрали подается на выходную магистраль.

Установка информационных триггеров в «0» обеспечивается входным управляющим сигналом R=0.

|

Уровень «1» на триггере запроса прерывания устанавливается при следующих входных сигналах: ЗП=С^(ВК1^ВК2); уровень «0» устанавливается при ЗП=RV (BK1 V ВК2).

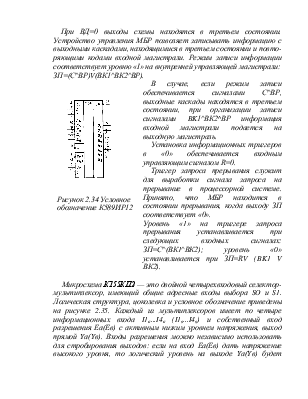

Микросхема К155КП2 — это двойной четырехвходовый селектор-мультиплексор, имеющий общие адресные входы выбора SO и S1. Логическая структура, цоколевка и условное обозначение приведены на рисунке 2.35. Каждый из мультиплексоров имеет по четыре информационных входа I1a...I4a (I1в...I4в) и собственный вход разрешения Ea(Ев) с активным низким уровнем напряжения, выход прямой Yа(Yв). Входы разрешения можно независимо использовать для стробирования выходов: если на вход Еа(Ев) дать напряжение высокого уровня, то логический уровень на выходе Yа(Yв) будет низким независимо от сигналов, действующих на информационных и адресных входах.

Если на вход Ea(Ев) подать напряжение низкого уровня, то в соответствии с кодом, набранным на адресных входах SO и 5/, разрешается работа только одного из информационных входов каждого селектора-мультиплексора. Табл. 6.1 дает состояния мультиплексора. То есть микросхема КП2 представляет собой четырехпозиционный переключатель на два направления, управляемый по двум адресным входам выбора, и функционирует согласно логическому уравнению:

У = E(I1S1SO + 12S1SO + I3S1SO + I4SISO).

Мультиплексор КП2 кроме обычных применений дает возможность:

автоматического распределения сигналов с любого информационного канала;

выбора одного из информационных каналов;

реализации логической функции параллельно-последовательного кодопреобразователя;

|

Выбор входа |

Входы |

Выход Y |

|||||

|

S0O |

S1 |

Е |

I1 |

I2 |

IЗ |

I4 |

|

|

X |

X |

1 |

X |

X |

X |

X |

0 |

|

0 |

0 |

а |

0 |

X |

X |

X |

0 |

|

0 |

0 |

0 |

1 |

X |

X |

X |

1 |

|

1 |

0 |

0 |

X |

0 |

X |

X |

0 |

|

1 |

0 |

0 |

X |

1 |

X |

X |

1 |

|

0 |

1 |

0 |

X |

X |

0 |

X |

0 |

|

0 |

1 |

0 |

X |

X |

1 |

X |

1 |

|

1 |

1 |

0 |

X |

X |

X |

0 |

0 |

|

1 |

1 |

0 |

X |

X |

X |

1 |

1 |

Таблица 2.2

Рисунок 2.35 Условное

обозначение К155КП2

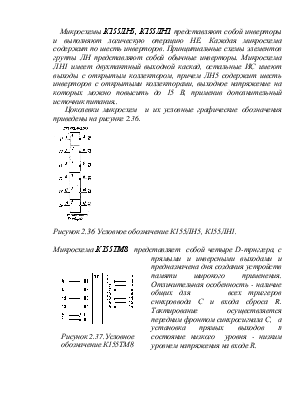

Микросхемы К155ЛН5, К155ЛН1 представляют собой инверторы и выполняют логическую операцию НЕ. Каждая микросхема содержит по шесть инверторов. Принципиальные схемы элементов группы ЛН представляют собой обычные инверторы. Микросхема ЛН1 имеет двухтактный выходной каскад, остальные ИС имеют выходы с открытым коллектором, причем ЛН5 содержит шесть инверторов с открытыми коллекторами, выходное напряжение на которых можно повысить до 15 В, применив дополнительный источник питания..

Цоколевки микросхем и их условные графические обозначения приведены на рисунке 2.36.

Рисунок 2.36 Условное обозначение К155ЛН5, К155ЛН1.

|

Микросхема

К155ТМ8 представляет собой четыре D-трнггера

Микросхема

К155ТМ8 представляет собой четыре D-трнггераУважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.