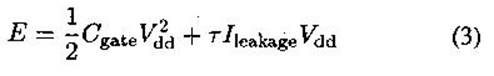

(здесь, Cgate - емкость вентиля, Vdd напряжение питания, и Ids-sat - поток насыщенности устройства) для устройства NMOS, полезного для оценки устройства6

3) Низкое энергопотребление. Цифровые схемы КМОП доминируют сегодня в значительной степени, потому что они могут выполнить любую функцию с меньшим количеством затраченной энергии чем любое другое семейство созданных устройств. У этого качества есть очевидная важность для приложений, использующих батареи, но оно также очень важно для систем, работающих от стены (щита), как способность рассеять высокую температуру всегда конечна. К первому заказу, в логическом шлюзе КМОП, энергия, расходуемая во время перехода, состоит в том, где Ileakage - ток утечки.

Полезные

метрики инергии включают инергию переключения устройств ![]() и статическую мощность спящего режима

устройства

и статическую мощность спящего режима

устройства ![]() . Для

ожидаемых 10 нм-ых длин шлюзов высокоэффективных транзисторов эти метрики могут

быть вычислены как 2 pJ и 1.1.·10-7, Вт,

соответственно.

. Для

ожидаемых 10 нм-ых длин шлюзов высокоэффективных транзисторов эти метрики могут

быть вычислены как 2 pJ и 1.1.·10-7, Вт,

соответственно.

Очень полезная метрика, которая объединяет последние два пункта выше, и дополнительно предотвращает "обман" (бесполезного) улучшения одной метрики взамен ухудшения другой, продукт задержки энергии. Для устройства это может измеряться как продукт свойственного постоянного времени скорости переключения и устройства, переключающего энергию, приблизительно 10-29 Дж s для быстродействующего устройства на 10 нм.

Молекулярные схемы сталкиваются со многими трудностями при соединении, или превышении, эти метрики, основанные на ограничениях нанопроизводства, описаны ранее. Многие из этих трудностей появляются из-за ограничений использования устройств с двумя терминалами. Устройства с двумя терминалами естественно не приводят к схемам, у которых есть усиление и хорошие свойства импеданса входа/выхода. Текущие устройства могут извлечь выгоду из лучшего отношения вкл\выкл, лучшая проводимость когда включено, и большее колебание напряжения когда выключено, чем в настоящее время демонстрируются. 7.КМОП достигает низкого энергопотребления в значительной степени, потому что небольшой ток течет на землю. Этот результат намного труднее достигнуть с двухтерминальными устройствами.

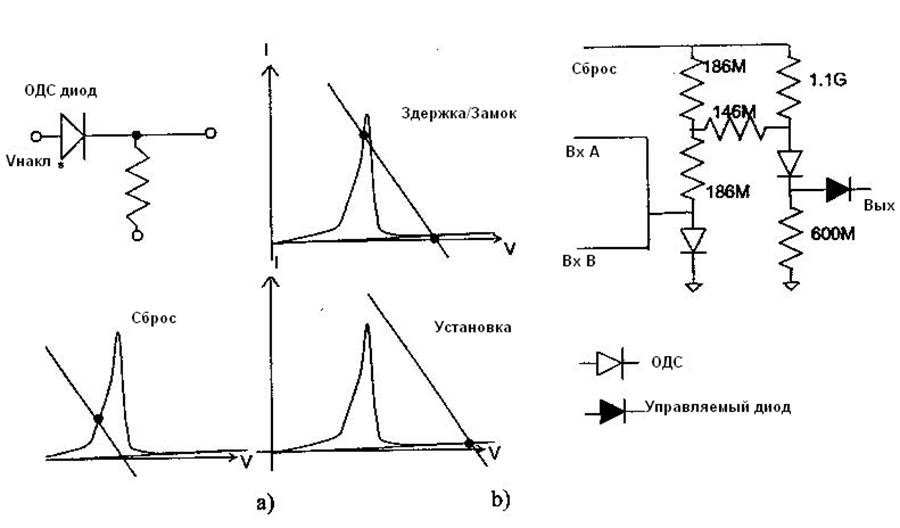

Рис. 8. (a) замок ОДС, используется в схемах памяти, и основе любой операции. (b) ОДС-на-основе вентиля НЕ - И.

5Международный Технологический сборник для Полупроводников (ITRS) [21] обеспечивает хороший поиск, описывая ожидаемые будущие способности КМОП.

6ITRS предсказывает = 0.15 пс для устройств с высокоэффективным шлюзом длиной 10 нм.

7Как бы то ни было ожидается улучшение устройств.

B. схемы ТД.

Как описано выше, замок может быть построен, используя устройство, показывая особенность ОДС, напоминающую о ТД. Принцип действия замка ОДС, когда он используется в качестве памяти, показан на рис. 8. Устройство ОДС нагружено резистором и, таким образом, может быть понято как простая линия анализа нагрузки. Устройство может быть переведено в высокое или низкое состояние, изменяя напряжение наклона. На промежуточном наклоне оно остается в предыдущем состоянии. Полезность этой схемы показана на рис. 6, несколько ограничена, главным образом плохой изоляцией входа-выхода из-за резистора, соединяющего вход и выход. Эта схема может поддержать только разветвление одного и имеет низкий шумовой дипазон. С другой стороны, замки на основе ОДС с изоляцией входа-выхода и большим разветвлением, чем каждая могла быть моделирована.

Замок представленный на рис. 8 (а) может быть изменен как показано на рис. 8 (б), чтобы позволить «НЕ-И» и «НЕ-ИЛИ» функции, которые позволяют подходящие цифровые особенности [39], [40]. Эта схема основана на устройствах, как продемонстрировано в [4], [41], и [42], и работает следующим образом. Такты применяются к линии «сброса» в резисторном мосте не протекает ток. После того, как такты замедляются, оба ОДС переходят в состояние высокого тока, низкого напряжения, низкого сопротивления. Как только входной ток увеличивется, напряжение на резисторном мосте увеличивется, добавляя ток к следующему состоянию ОДС. Резисторы изменены таким образом, что входной пороговый ток в точке, которая объединяет ток моста вызывающий переход на вторую стадию состояния ОДС к низкому току, высокому напряжению (высокому импедансу).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.