Лекция 6

УСТРОЙСТВА, КОТОРЫЕ ОБЛАДАЮТ ПАМЯТЬЮ

Тема 6.1 Триггеры

План:

1 Общие сведения и классификация;

2 Виды триггеров.

1 Триггер ( TriggerFlip-Fop) – электронное устройство, которое является важным элементом и лежит в основе построения больших и средних ИС: регистры, счетчики, память и микропроцессор.

Триггер – это элементарный цифровой автомат, который содержит ячейку памяти и хранит в нем 1 бит информации (логический ноль или логическая единица).

Триггер – это спусковое устройство, которое может находится в одном из двух устойчивых состояний и переходит из одного состояния в другое под действием внешнего входного сигнала.

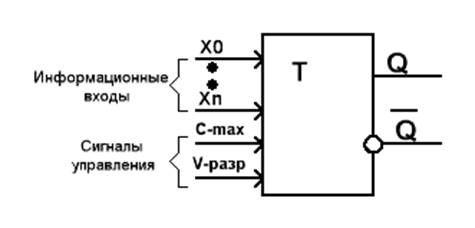

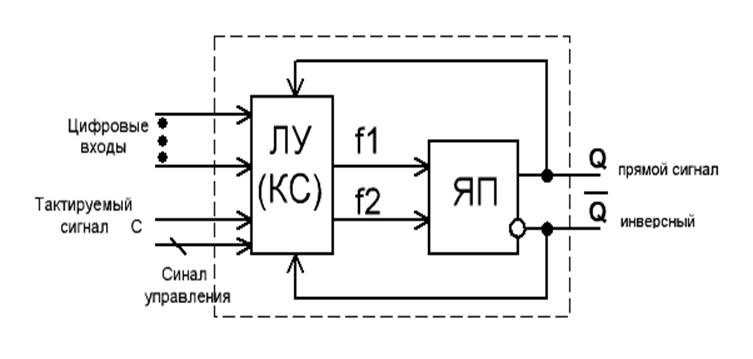

УГО:

Рисунок 6.1 – Структурная схема триггера

ЛУ (КС) – логическое устройство (комбинационная схема) – схема управления;

ЯП – ячейка памяти (сам триггер);

Информационные входы – изменяют состояние триггера;

Сигналы управления:

- вход Clock – тактируемый вход и по приходу импульсов на этот вход триггер изменяет свое состояние;

- сигнал Volve – сигнал разрешения либо на приход, либо на выдачу информации.

Q, Q – выходы прямой инверсный. Все рассуждения работы триггера ведутся относительно прямому выходу (Q).

Классификация:

1 По элементной базе:

- на биполярных и полевых транзисторах;

- на логических элементах;

- на целой интегральной схеме ТТЛ, КМОП и ТТЛШ структур;

2 По функциональному назначению:

0 1

- RSтриггер – имеет два раздельных входа с установкой в ноль и единицу (тип ТР);

- Т - триггер, который имеет один счетный вход и изменяет свое состояние на противоположное каждый раз, когда на его вход приходит логическая единица (не выпускаются как самостоятельная ИС);

- Dтриггер – триггер задержки (прозрачная защелка). Принимает информацию по 1 входу и сигнал на выходе повторяет сигнал на входе, но с определенной задержкой по приходу тактового сигнала (тип ТМ);

- DVиTVтриггеры – это сложные триггеры, которые имеют дополнительный управляющий вход V, где по приходу V = 1 DV и TV работают как D и Т триггеры; а по приходу V = 0 триггеры перестают воспринимать входную информацию и находятся в режиме хранения;

- JKтриггер – универсальный триггер с разделенной установкой логического нуля и логической единицы. В режиме 1.1 работает как Т триггер;

- Комбинированный триггер – совмещает несколько режимов работы триггера;

- Триггер со сложной входной логикой – в основном JK триггер, где J и K соединены конъюнкцией по каждому входу;

3 По способу управления:

- асинхронные;

- синхронные – делятся по уровню и по фронту (переднему и заднему), следовательно, переключается состояние триггера только по тактовому входу (по входу Clock). Применяется как самостоятельный элемент элементарной ячейки памяти; входит в состав регистров, счетчиков, ПЗУ.

2 Виды триггеров:

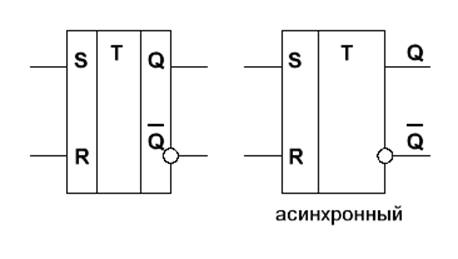

1 Триггер RS( тип ТР)

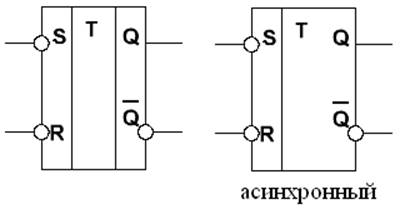

УГО:

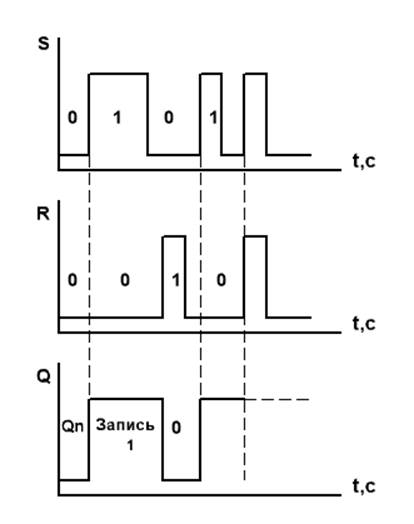

Таблица 6.1 – Таблица состояния

|

S |

R |

Qn+1 |

Режимы |

|

0 |

0 |

Qn |

Режим хранения |

|

1 |

0 |

1 |

Запись единицы |

|

0 |

1 |

0 |

Запись нуля |

|

1 |

1 |

Х |

Запрещенное состояние |

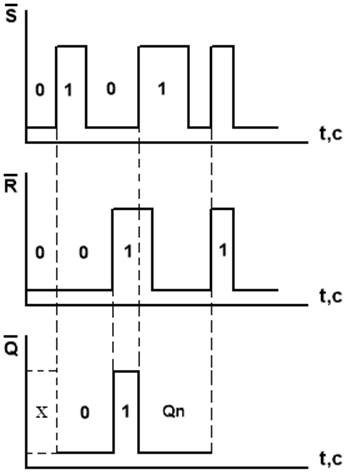

Рисунок 6.2 – Временные диаграммы

RS триггеры также строятся на логических элементах:

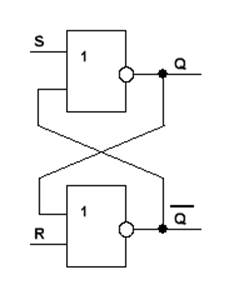

Рисунок 6.3 – RS триггер, построенный на логических элементах ИЛИ-НЕ (ЛЕ)

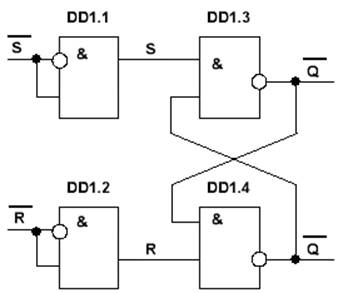

Рисунок 6.4 - RS триггер, построенный на логических элементах И-НЕ (ЛА)

2 Триггер RS

УГО:

![]() , где Qn+1 - новое состояние, Qn- предыдущее состояние.

, где Qn+1 - новое состояние, Qn- предыдущее состояние.

Таблица 6.2 – Таблица состояния

|

S |

R |

Qn+1 |

Режимы |

|||

|

0 |

0 |

Х |

Запрещенное состояние |

|||

|

1 |

0 |

0 |

Запись нуля |

|||

|

0 |

1 |

1 |

Запись единицы |

|||

|

1 |

1 |

Qn |

Режим хранения |

Рисунок 6.5 – Временные диаграммы

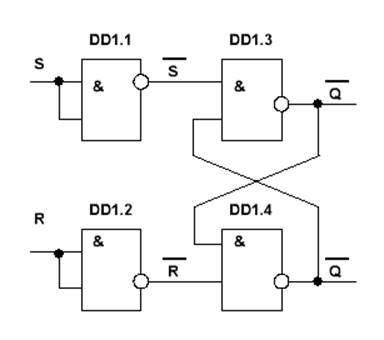

Рисунок 6.6 – RS триггер, построенный на элементах И-НЕ

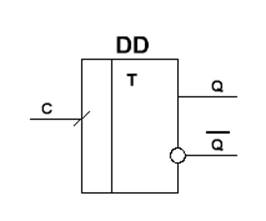

3 Счетный триггер Т – имеет особенность: изменяет свое состояние по приходу импульса на информационные входы. Триггер практически не имеет своей ИС и строится на D, JK и RS триггерах.

УГО:

Таблица 6.3 – Таблица состояния

|

Т |

Q n+1 |

|

0 |

Q n |

|

1 |

Q n |

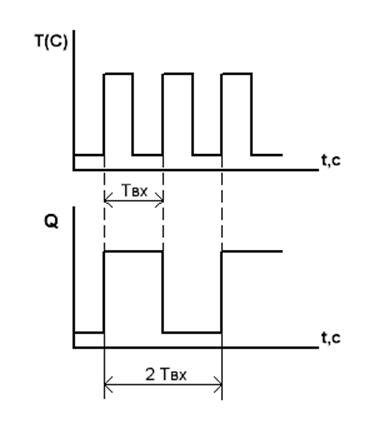

Рисунок 6.7 – Временные диаграммы

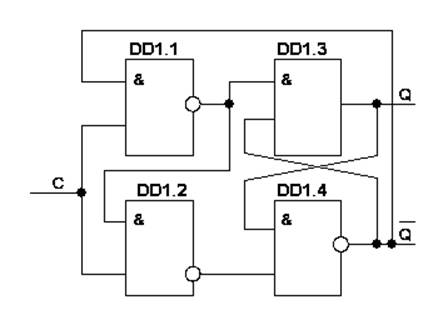

Рисунок 6.8 - Т триггер, построенный на логических элементах И-НЕ (тип К155ЛА, К555ЛА)

Счетный Т триггер еще называется делителем частоты на два.

Вывод: Т триггер служит для формирования меандры.

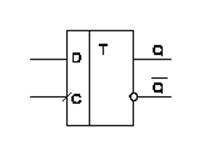

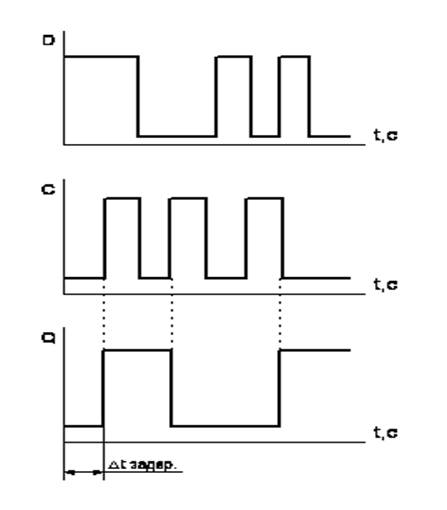

4 Dтриггер – управляется по информационному входу D, но переключение происходит не сразу, а с приходом тактового импульса Clock, следовательно, D триггер повторяет на выходе тот же сигнал , что и на входе, но с некоторой задержкой, так называемая «прозрачная защелка» - триггер задержки. Тип ТМ.

УГО:

![]()

![]() Qn+1

= DC + Qn * C

Qn+1

= DC + Qn * C

Таблица 6.4 – Таблица состояния

|

D |

C |

Q n+1 |

|

0 |

0 |

Q n |

|

1 |

0 |

|

|

0 |

1 |

0 |

|

1 |

1 |

1 |

Рисунок 6.9 – Временные характеристики

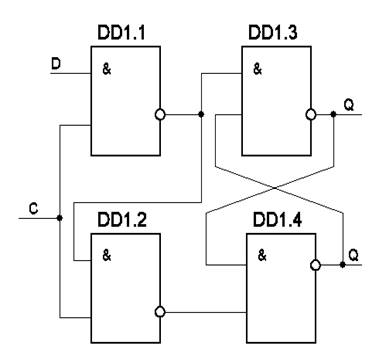

Рисунок 6.10 – Построение Т триггера на логических элементах И-НЕ

Рисунок 6.11 – Построение Т триггера на Dтриггере, D→Т

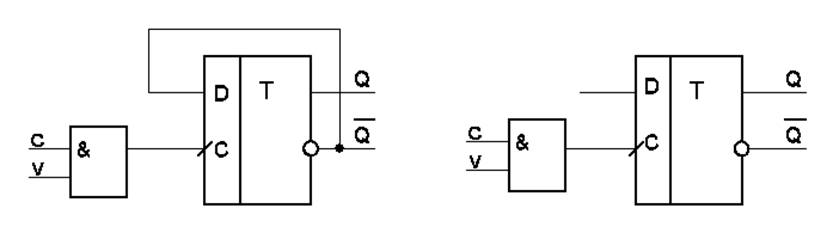

5 DV и TVтриггеры – ко входу Clock подключен логический элемент И.

УГО:

TV триггер DV триггер

Сигнал V– сигнал управления (разрешение). Если V=1, то работает как D триггер, при условии, если на вход С приходит 0 или 1. Если V=0, то DV триггер не переключается независимо от прихода информации на вход D. По такому же принципу работает TV триггер.

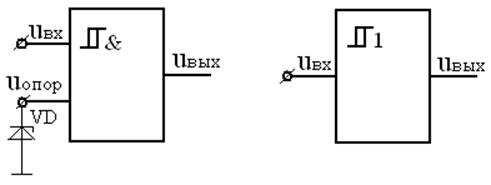

6 Триггер Шмидта – это элемент, который преобразует медленно изменяющийся аналоговый сигнал в импульсный путем сравнения входной величины с опорным напряжением. Имеет тип ТЛ.

УГО:

Рисунок 6.12 – Временные характеристики

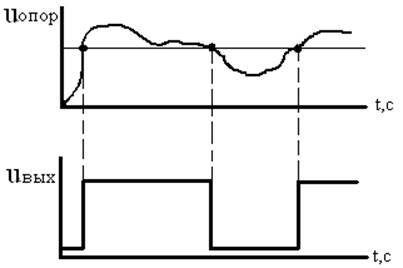

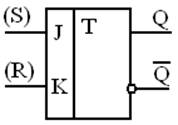

7 JK триггер (универсальный) – аналогичен работе RS триггера.

JK триггер – это триггер, который не имеет запрещенного состояния, т.е. при поступлении на вход триггеров Jи K, равные логической единице, триггер переключается в противоположное состояние по отношению к предыдущему состоянию. Имеет тип ТР.

УГО:

Qn+1 = JQn + K * Qn

Таблица 6.5 – Таблица состояния

|

J |

K |

Qn+1 |

|

0 |

0 |

Qn |

|

1 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

1 |

Qn |

![]()

Qn – противоположно предыдущему состоянию.

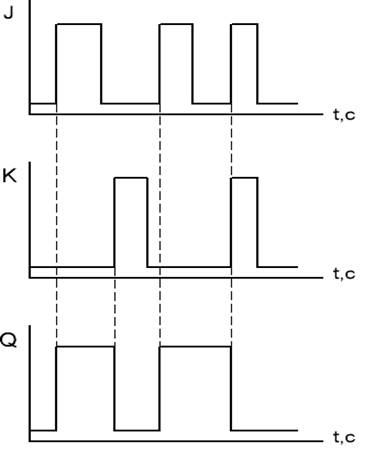

Рисунок – 6.13 – Временные характеристики

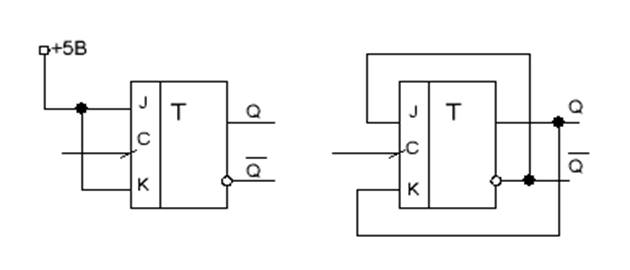

а) б)

а)- построение Т триггера на JK, б) – построение Т триггера с обратной связью

Рисунок 6.14

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.