Санкт-Петербургский Государственный Политехнический Университет

Факультет Технической Кибернетики

Кафедра Автоматики и Вычислительной Техники

ОТЧЕТ

о лабораторной работе №3.

Тема: Триггеры.

|

Выполнил студент |

гр. 3081/2 А |

|

Преподаватель |

___________ |

Санкт-Петербург

2009 г.

1. Задание.

Ø В САПР Quartus II выполните ввод схемы асинхронного RS-триггера, функциональная схема и условное изображение которого приведены на Рис. 1. Выполните компиляцию проекта для СБИС ПЛ указанного преподавателем семейства. Обратите внимание на предупреждение компилятора о наличии комбинаторных обратных связей (combinatorial loops) в схеме. В обычной практике наличие таких связей говорит об ошибке в проекте.

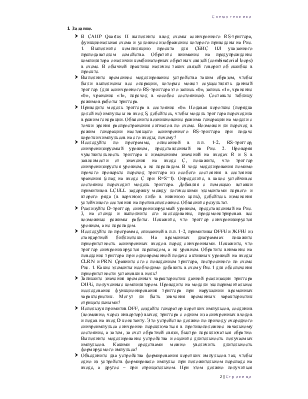

Ø Выполните временное моделирование устройства таким образом, чтобы были выполнены все операции, которые может осуществлять данный триггер. (для асинхронного RS-триггера это запись «0», запись «1», хранение «0», хранение «1», переход в «особое состояние»). Составьте таблицу режимов работы триггера.

Ø Приведите модель триггера в состояние «0». Подавая короткие (порядка долей нс) импульсы на вход S, добейтесь, чтобы модель триггера переходила в режим генерации. Объясните возникновение режима генерации на модели с точки зрения распространения сигналов по схеме. Возможен ли переход в режим генерации настоящего асинхронного RS-триггера при подаче коротких импульсов на его входы, почему?

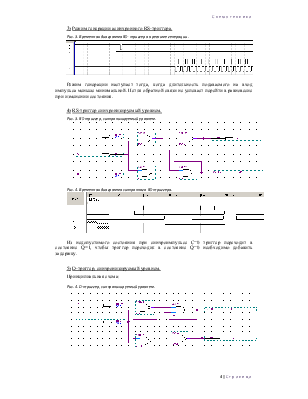

Ø Исследуйте по программе, описанной в п.п. 1-2, RS-триггер, синхронизируемый уровнем, представленный на Рис. 2. Проверяя чувствительность триггера к изменениям значений на входах R и S в зависимости от значения на входе C, покажите, что триггер синхронизируется уровнем, а не перепадом. В ходе моделирования помимо прочего проверьте переход триггера из особого состояния в состояние хранения (спад на входе С при R=S=1). Определите, в какое устойчивое состояние переходит модель триггера. Добавляя с помощью вставки примитивов LCELL задержку между логическими элементами первого и второго ряда (в верхнюю либо в нижнюю цепь), добейтесь изменения устойчивого состояния на противоположное. Объясните результат.

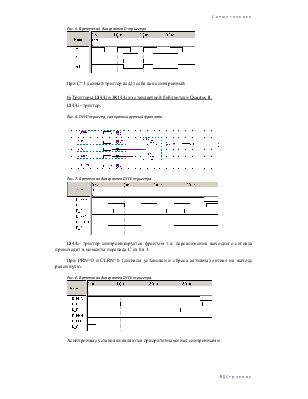

Ø Реализуйте D-триггер, синхронизируемый уровнем, представленный на Рис. 3, на стенде и выполните его исследование, продемонстрировав все возможные режимы работы. Покажите, что триггер синхронизируется уровнем, а не перепадом.

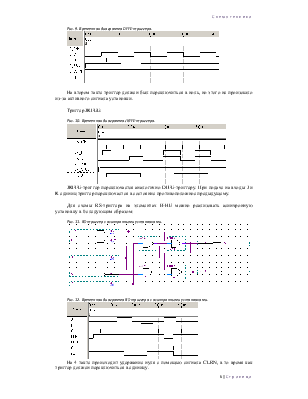

Ø Исследуйте по программе, описанной в п.п. 1-2, примитивы DFFE и JKFFE из стандартной библиотеки. На временных диаграммах покажите приоритетность асинхронных входов перед синхронными. Покажите, что триггер синхронизируется перепадом, а не уровнем. Обратите внимание на поведение триггера при одновременной подаче активных уровней на входы CLRN и PRN. Сравните его с поведением триггера, построенного по схеме Рис. 1. Какие элементы необходимо добавить в схему Рис.1 для обеспечения приоритетности установки в ноль?

Ø Запишите значения временных характеристик данной реализации триггера

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.