САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ ПОЛИТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

ФАКУЛЬТЕТ ТЕХНИЧЕСКОЙ КИБЕРНЕТИКИ

КАФЕДРА АВТОМАТИКИ И ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ

по лабораторной работе №5

«Двоичные и двоично-десятичные счетчики»

Работу выполнил студент 3081/2

группа ФИО

Преподаватель

подпись ФИО

Санкт-Петербург

2006г.

Цель работы

Исследование работы счётчиков К155ИЕ5 и К155ИЕ7, выполненных в виде ИС, а также счётчиков, реализованныx на элементах СБИС ПЛ средствами САПР Quartus II с использованием конфигурируемых библиотечных модулей.

Выполнение работы

1. Исследование 4-разрядного асинхронного счетчика К155ИЕ5

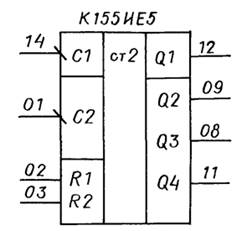

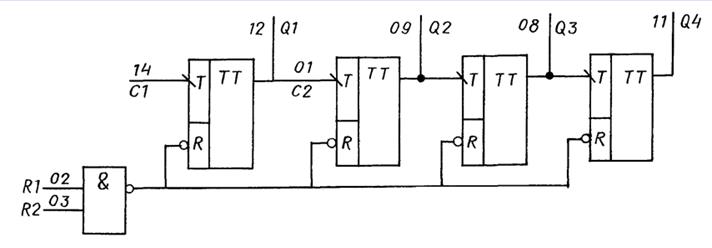

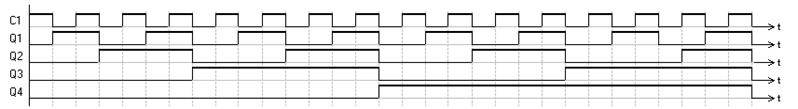

Условное изображение счетчика К155ИЕ5 приведено на рис. 1. На рис. 2 приведена функциональная схема 4-разрядного счетчика, который получается путем внешнего соединения Q1 и С2. Временные диаграммы работы построенного на базе К155ИЕ5 четырехразрядного счетчика приведены на рис. 3.

Рис. 1. Условное изображение счетчика К155ИЕ5.

Рис. 2. Функциональная схема четырехразрядного счетчика, построенного на базе К155ИЕ5.

Рис. 3. Временные диаграммы работы четырехразрядного счетчика, построенного на базе К155ИЕ5.

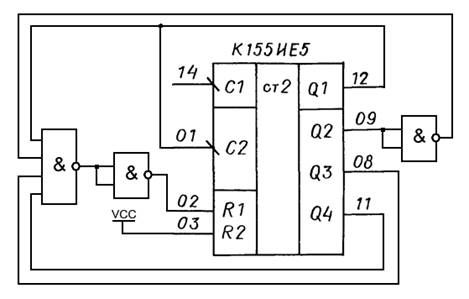

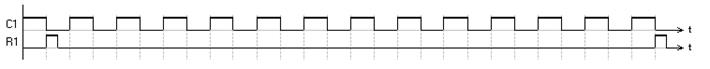

На базе счетчика К155ИЕ5 была разработана схема делителя частоты на 13. Схема делителя приведена на рис. 4, временная диаграмма сигнала R1, по которому производится сброс делителя частоты, приведена на рис. 5.

Рис. 4. Схема делителя частоты на 13, построенного на базе счетчика К155ИЕ5.

Рис. 5. Временная диаграмма сигнала R1, по которому производится сброс делителя.

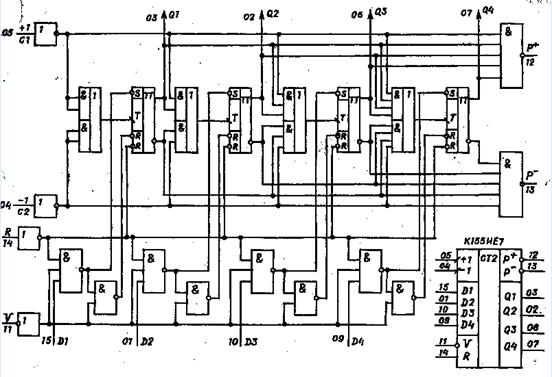

2. Исследование 4-разрядного реверсивного двоичного счетчика К155ИЕ7

Условное изображение и функциональная схема счетчика К155ИЕ7 приведены на рис. 6. Временные диаграммы работы счетчика К155ИЕ7 приведены на рис. 7.

Рис. 6. Условное изображение и функциональная схема счетчика К155ИЕ7.

Рис. 7. Временные диаграммы работы счетчика К155ИЕ7.

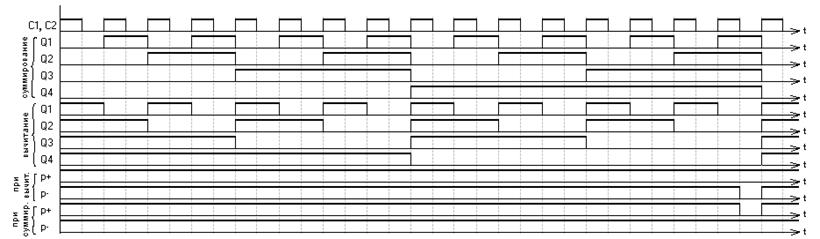

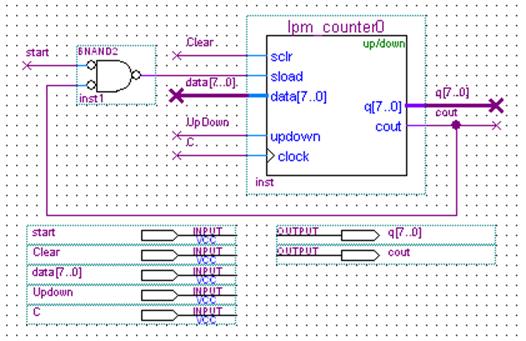

3. Исследование счетчиков, построенных на СБИС ПЛ

Для реализации счетчика использовалась мегафункция LPM_COUNTER, на микросхемах семейства MAX3000A. Исследование производилось в САПР Quartus II.

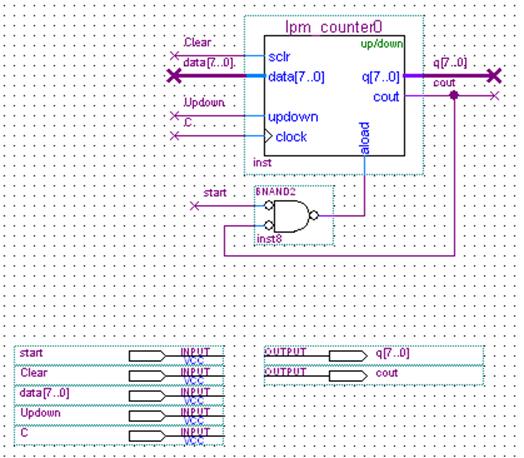

Схема делителя частоты на произвольное число КД=1-255

КД=13

Схема делителя изображена на рис. 8.

Рис. 8. Схема делителя частоты на 13, реализованная в САПР Quartus II.

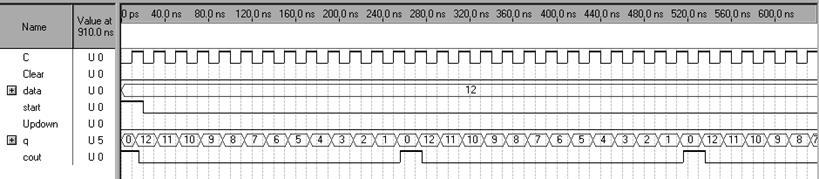

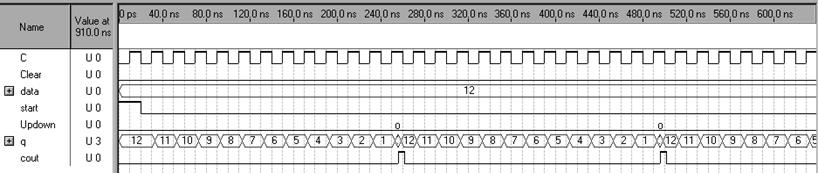

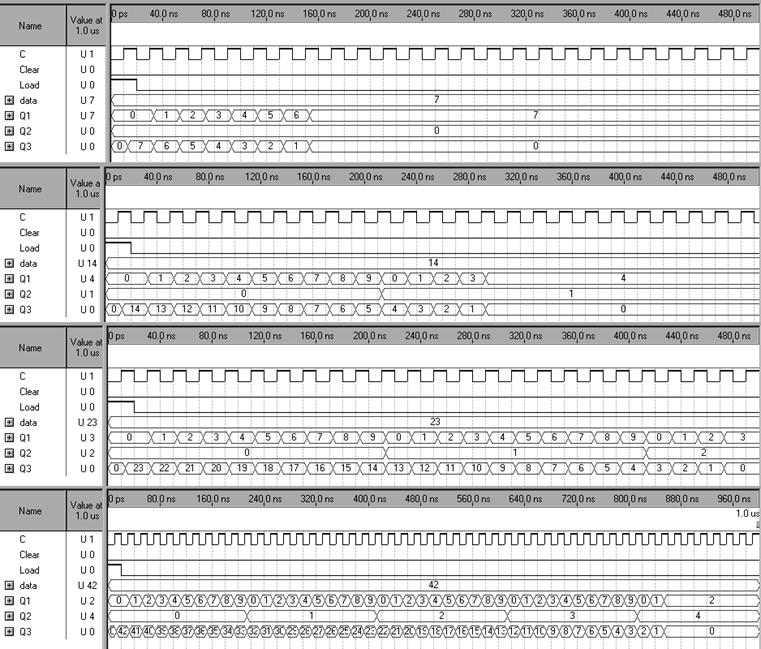

Работа счётчика реализована в

двух вариантах: в первом варианте ![]() -1

подаётся на входы data[7..0], счётчик при этом работает

в режиме вычитания (временные диаграммы работы делителя приведены на рис. 9).

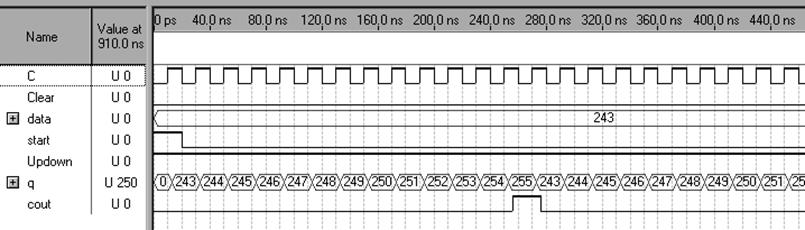

Второй вариант: 256 -

-1

подаётся на входы data[7..0], счётчик при этом работает

в режиме вычитания (временные диаграммы работы делителя приведены на рис. 9).

Второй вариант: 256 -![]() подаётся

на вход data[7..0], счётчик работает в режиме сложения

(временные диаграммы работы делителя приведены на рис. 10).

подаётся

на вход data[7..0], счётчик работает в режиме сложения

(временные диаграммы работы делителя приведены на рис. 10).

Рис. 9. Временные диаграммы работы делителя частоты на 13, работающего по первому варианту.

Рис. 10. Временные диаграммы работы делителя частоты на 13, работающего по второму варианту.

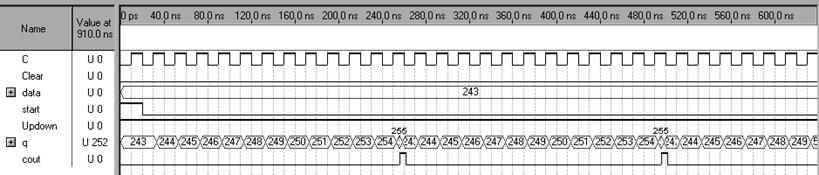

Схема делителя частоты с использованием асинхронной загрузки и временные диаграммы работы по двум вариантам представлены на рис. 11-13.

Рис. 11. Схема делителя частоты на 13 с использованием асинхронной загрузки, реализованная в САПР Quartus II.

Рис. 12. Временные диаграммы работы делителя частоты на 13 с использованием асинхронной загрузки, работающего по первому варианту.

Рис. 12. Временные диаграммы работы делителя частоты на 13 с использованием асинхронной загрузки, работающего по второму варианту.

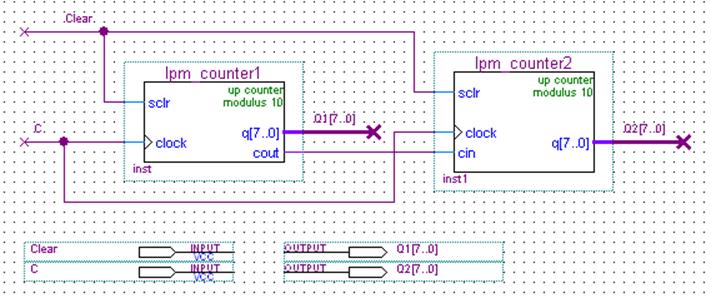

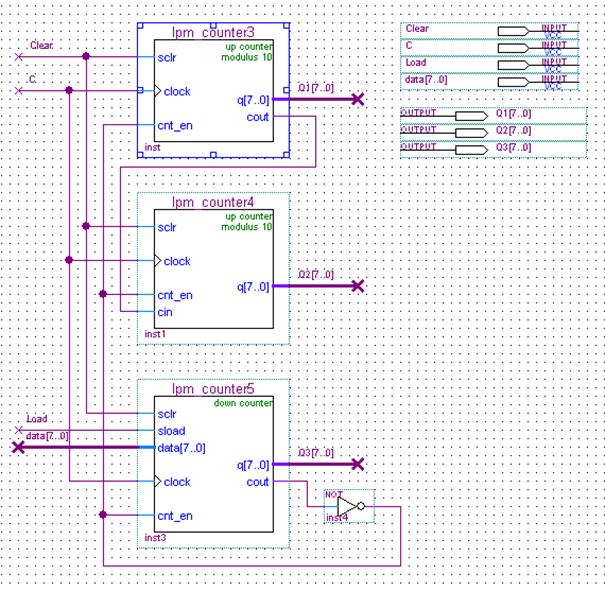

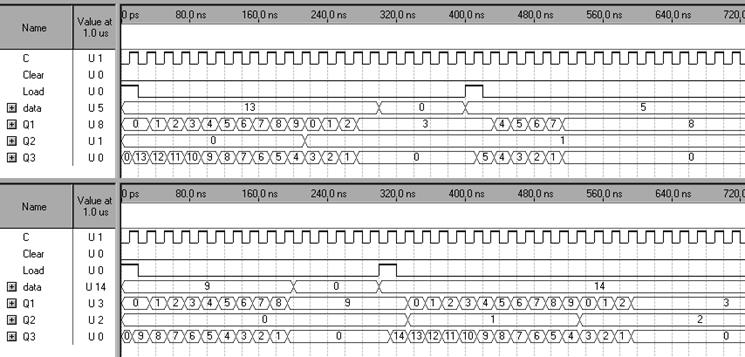

Схема двухтетрадного двоично-десятичного счётчика

Схема, построенная из двух счётчиков с модулем счёта 10, представлена на рис. 14.

Временные диаграммы работы счетчика представлены на рис. 15.

Рис. 14. Схема двухтетрадного двоично-десятичного счетчика, построенная в САПР Quartus II.

Рис. 15. Диаграммы работы двухтетрадного двоично-десятичного счетчика.

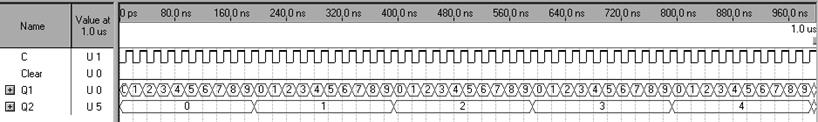

Схема преобразователя двоичного кода в двоично-десятичный

Схема преобразователя и временные диаграммы работы приведены на рис. 16, 17.

Рис. 16. Схема преобразователя двоичного кода в двоично-десятичный, построенная в САПР Quartus II.

Рис. 17. Временные диаграммы работы преобразователя двоичного кода в двоично-десятичный при различных входных данных.

Схема накапливающего сумматора

Схема накапливающего сумматора совпадает со схемой преобразователя двоичного кода в десятичный. Временные диаграммы работы сумматора приведены на рис. 18.

Рис. 18. Временные диаграммы работы сумматора.

Выводы

1. Исследование 4-разрядного счётчика К155ИЕ5

На рис. 3. показаны все значения выходов, которые может принимать 4-разрядный счетчик на базе К155ИЕ5, от 0 до 15.

Делитель, построенный на основе счётчика К155ИЕ5, производит деление частоты синхроимпульсов на 13. На рис. 5 видно, что за один период появления R1 появляется 13 синхроимпульсов, поэтому можно говорить, что схема построена правильно.

2. Исследование 4-разрядного реверсивного счётчика К155ИЕ7

Была рассмотрена работа счетчика в режиме счёта (V=1, R=0) на сложение (С1=CLK, C2=1), на вычитание (С1=1, C2= CLK). В режиме счёта на сложение на выходе переноса P+ формируется импульс отрицательной полярности при Q=15 (1111), выход заёма Р- =1. При счёте на вычитаниеP+ =1, а на выходе Р- импульс отрицательной полярности формируется при Q=0 (0000). Длительность импульса переноса и заёма равна времени паузы синхросигнала.

3.Исследование счётчиков, построенных на СБИС ПЛ

Схема делителя частоты на произвольное число КД=1-255

Схема делителя

была реализована по двум вариантам. Рис. 9 и 10 демонстрируют работу

делителя при ![]() =13,

т.е. за один период выходного сигнала "cout"

формируется 13 синхроимпульсов.

=13,

т.е. за один период выходного сигнала "cout"

формируется 13 синхроимпульсов.

В схеме с асинхронной загрузкой время импульса выходного сигнала "Out" меньше, чем при синхронной загрузке, но время периода не меняется. Делитель работает правильно.

Схема двухтетрадного двоично-десятичного счётчика

Для реализации схемы были использованы счётчики с модулем счёта 10. При этом перенос в младший разряд второго счётчика (который отвечает за "десятки") производился при формировании переноса из старшего разряда первого счётчика ("единицы"). Таким образом, была получена схема двухтетрадного двоично-десятичного счётчика, на выходе которой могут быть получены значения 0-99.

Схема преобразователя двоичного кода в двоично-десятичный

Для реализации схемы были использованы двухтетрадный двоично-десятичный счётчик на сложение и двоичный 8-разрядный счётчик на вычитание. В схеме был использован импульс запуска ("LOAD"), при формировании которого в начале работы преобразователя в двоичный счётчик загружается преобразуемый код. Как только формируется перенос из старшего разряда в двоичном счетчике, на выходе двоично-десятичного счетчика получается преобразованный код. Ввиду того, что запрещение счета производится по низкому уровню, на выходе переноса из старшего разряда использован инвертор.

Схема накапливающего сумматора

В данной схеме производится последовательное преобразование двоичного кода в двоично-десятичный без сброса в "0" после каждого преобразования. Очередное слагаемое подается при подаче импульса со входа Load. Частота этих импульсов зависит от чисел, которые суммируются – если нужно дождаться, когда счетчик досчитает до нужного значения. Если слагаемые неизвестны, то придется рассчитывать время между слагаемыми, исходя из максимального значения – 100 тактов.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.