Санкт-Петербургский Государственный Политехнический Университет

_____________________________________________________________________________

Факультет Технической Кибернетики

Кафедра Автоматики и Вычислительной Техники

Отчет

по лабораторной работе

Регистры и сумматоры

Схемотехника

Работу выполнила:

группа 3081/2

Работу принял:

Подпись преподавателя:___________________

Санкт-Петербург

2009

1. Цель работы:

Исследовать различные регистры и сумматоры, исследовать работу мегафункции LPM_SHIFTREG, LPM_ADD_SUB.

2. Выполнение работы.

Регистры

2.1 Исследование 8-разрядного сдвигающего регистра и мегафункции LPM_SHIFTREG.

Рис 2.1.1 8-разрядный сдвигающий регистр в QuartusII

входы:

aclr – асинхронный сброс (для того, чтобы изначально установить во все 0)

clock – синхровход; переключение по фронту

enable– режим хранения при «0», при «1» - загрузка и сдвиг данных

load – режим работы: «1» - параллельная загрузка, «0» - сдвиг. По умолчанию – сдвиг.

shiftin – данные для последовательной загрузки; по умолчанию «1».

data[7..0] – данные для синхронной параллельной загрузки, имеет разрядность LPM_WIDTH (8).

выход:

q[] – состояние регистра, имеет разрядность LPM_WIDTH (8).

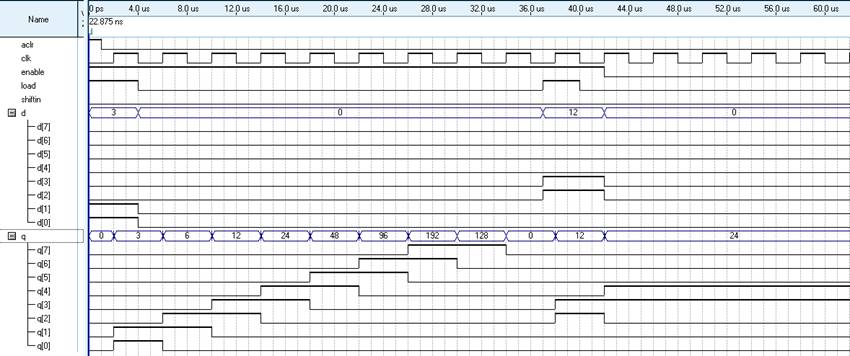

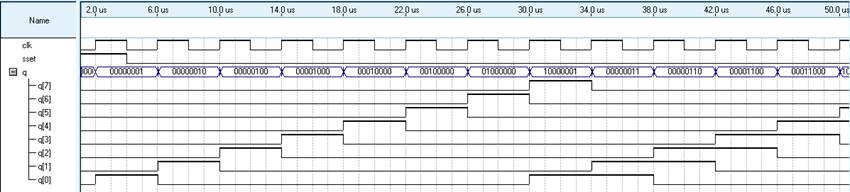

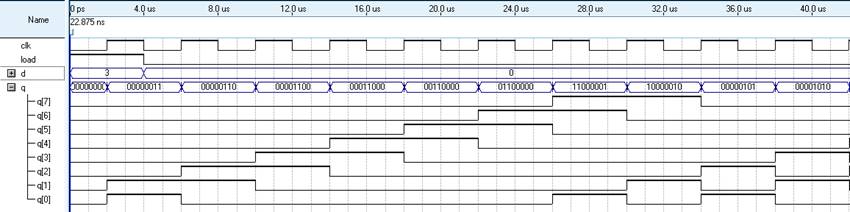

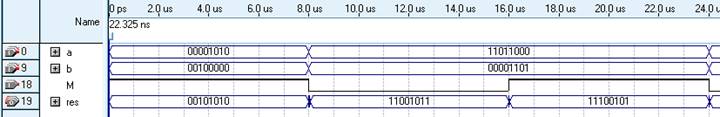

Рис 2.1.2 Моделирование работы регистра в QuartusII

Из временной диаграммы видно, что регистр загружает и сдвигает данные при значении load = 1, если загрузка разрешена (1 на enable), и хранит загруженные данные, если он установлен в режим хранения (0 на enable).

2.2 Исследование регистра, позволяющего загружать информацию и сдвигать ее в обоих направлениях на базе мегафункции LPM_SHIFTREG.

2.3 Исследование счетчика Джонсона на базе мегафункции LPM_SHIFTREG.

Ставим инвертор в обратную связь схемы.

Рис 2.3.1 Счетчик Джонсона в QuartusII

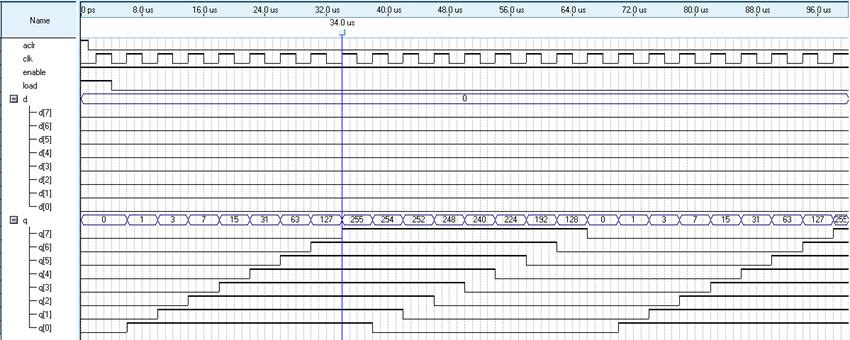

Рис 2.3.2 Моделирование работы счетчика Джонсона в QuartusII

2.4 Исследование генератора псевдослучайных двоичных чисел на базе мегафункции LPM_SHIFTREG.

В цепь обратной связи включается схема xor.

Рис 2.4.1 Генератор псевдослучайных чисел в QuartusII

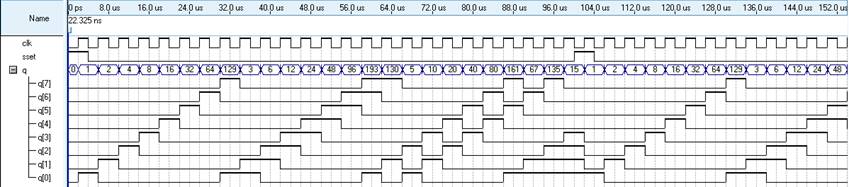

sset– синхронная установка в 1, устанавливает регистр в 1 по положительному перепаду синхровхода

Рис 2.4.2 Моделирование работы генератора случайных чисел в QuartusII, первый вариант. Разные масштабы

Теперь будем загружать в регистр двоичное число с входов data.

Рис 2.4.3 Генератор псевдослучайных чисел в QuartusII

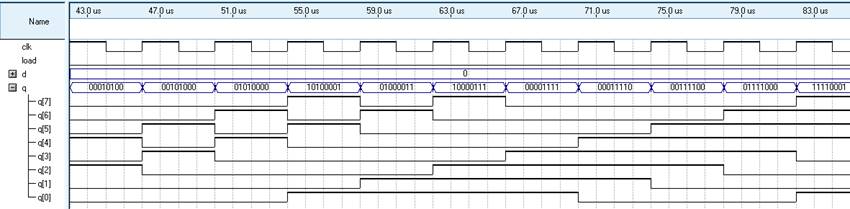

Рис 2.4.4 Моделирование работы генератора случайных чисел в QuartusII, второй вариант, загрузка двоичного числа. Диаграмма от 0 до 42 и от 42 до 85 мксек.

Передаваемый сигнал смешивается с псевдослучайными сигналами.

Сумматоры

2.5 Исследование сумматора-вычитателя и мегафункции LPM_ADD_SUB.

Рассмотрим сумматор-вычитатель в дополнительном коде.

Рис 2.5.1 Сумматор-вычитатель в дополнительном коде в QuartusII

входы:

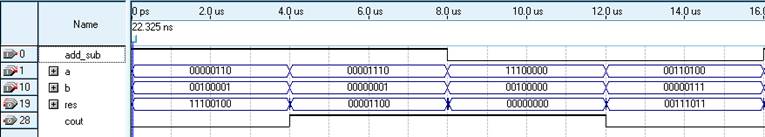

add_sub – режим работы: 1 – сложение, 0 - вычитание

data[7..0] – первое слагаемое/уменьшаемое, имеет разрядность LPM_WIDTH (8)

datab[7..0] – второе слагаемое/вычитаемое, имеет разрядность LPM_WIDTH (8).

выход:

result[7..0] – результат операции, имеет разрядность LPM_WIDTH (8).

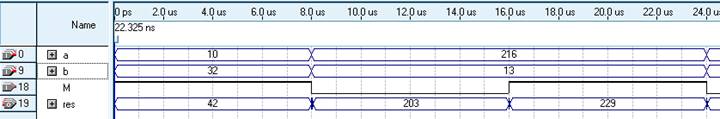

Аргументы a и b поступают на вход сумматора в дополнительном коде, результат также получается в дополнительном коде.

Рис 2.5.2 Моделирование работы сумматора-вычитателя в QuartusII, десятичная система счисления

Рис 2.5.3 Моделирование работы сумматора-вычитателя в QuartusII, двоичная система счисления

Рассмотрим сумматор-вычитатель в обратном коде.

Рис 2.5.4 Сумматор-вычитатель в обратном коде в QuartusII

cin – разряд входного переноса. При переполнении сумматор формирует разряд выходного переноса cout.

При выполнении сложения: 0 – переноса не было, 1 – перенос был, при выполнении вычитания: 0 – заем был, 1 - заема не было.

Рис 2.5.5 Моделирование работы сумматора-вычитателя в обратном коде в QuartusII

2.6 Исследование одного разряда двоично-десятичного сумматора

3. Выводы.

Схема делителя частоты на произвольное число КД=1-255

Схема делителя была реализована по двум вариантам.

Рис. 9 и 10 демонстрируют работу делителя при ![]() =13,

т.е. за один период выходного сигнала "cout"

формируется 13 синхроимпульсов.

=13,

т.е. за один период выходного сигнала "cout"

формируется 13 синхроимпульсов.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.