Запись производится при нажатии кнопки ЗАГРУЗКА, при этом можно проверить содержимое ЗУМК по индикаторам ПАМЯТЬ.

2. При нажатии кнопки ПУСК в режиме ЗАГРУЗКА происходит сброс счётчика адресов на адрес, указанный на клавишном регистре АДРЕС (для выполнения программы сначала необходимо установить начальный адрес).

3. Для выполнения микропрограммы переключатель ЗАГРУЗКА/РАБОТА устанавливается в положение РАБОТА. Перед этим необходимо проверить, что тумблер задания тактирования ШАГ/АВТОМАТ включён в положение ШАГ. Для выполнения микропрограммы тактовые импульсы подаются при нажатии кнопки ПУСК.

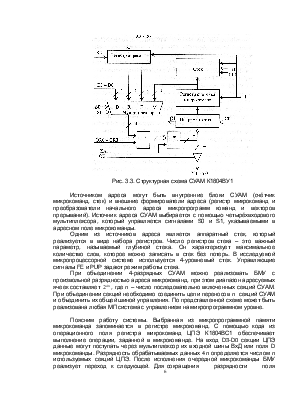

В стенде используется 32-разрядный формат микрокоманды, представленный на рис.3.6. Номера тетрад однозначно связаны с положением переключателя управления мультиплексором.

|

Разряды |

|||||||||||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

||||

|

31-28 |

27-24 |

23 |

22-20 |

19 |

18-16 |

15 |

14-12 |

11-8 |

7-4 |

3-0 |

|

|

Значение |

Адрес перехода |

Инструкции перехода |

MS2 |

Приёмник результата |

MS1 |

Источник операндов |

C0 |

АЛУ |

A |

B |

D |

Рис. 3.6. Формат микрокоманды, используемый в микротренажере МТ1804

Адресная часть включает в себя тип перехода и адрес перехода (при необходимости), коды инструкций перехода (Р3-Р0) приведены в таблице 3.1.

Таблица 3.1

|

Код инструкции перехода |

Тип перехода |

||||

|

Р3 |

Р2 |

Р1 |

Р0 |

||

|

0 |

0 |

0 |

0 |

Переход на адрес из регистра микрокоманд, если Z=0 |

|

|

0 |

0 |

0 |

1 |

Переход на адрес из регистра микрокоманд |

|

|

0 |

0 |

1 |

0 |

Продолжить (переход на следующий адрес) |

|

|

0 |

0 |

1 |

1 |

Переход на адрес, формируемый клавиным регистром адреса (переход на адрес вектора) |

|

|

0 |

1 |

0 |

0 |

Переход к подпрограмме, если Z=0 |

|

|

0 |

1 |

0 |

1 |

Переход к подпрограмме |

|

|

0 |

1 |

1 |

0 |

Возврат из подпрограммы |

|

|

0 |

1 |

1 |

1 |

Переход по стеку |

|

|

1 |

0 |

0 |

0 |

Окончить цикл и вытолкнуть из стека, если Z=1 |

|

|

Таблица 3.1. (окончание) |

|||||

|

1 |

0 |

0 |

1 |

Загрузить стек и продолжить |

|

|

1 |

0 |

1 |

0 |

Вытолкнуть из стека и продолжить |

|

|

1 |

0 |

1 |

1 |

Окончить цикл и вытолкнуть из стека |

|

|

1 |

1 |

0 |

0 |

Переход на адрес из регистра микрокоманд, если Z=1 |

|

|

1 |

1 |

0 |

1 |

Переход на адрес из регистра микрокоманд, если F3=1 |

|

|

1 |

1 |

1 |

0 |

Переход на адрес из регистра микрокоманд, если OVR=1 |

|

|

1 |

1 |

1 |

1 |

Переход на адрес из регистра микрокоманд, если С4=1 |

|

Разряды 23 и 19 микрокоманды, обозначенные как MS1 и MS2, задают тип сдвига (MS2 MS1):

· 00 - сдвиг 4-разрядного слова с вводом лог.0 в старшие (младшие) разряды РОН и регистр Q;

· 01 – циклический сдвиг 4-разрядного слова;

· 10 – циклический сдвиг 8-разрядного слова;

· 11 – арифметический сдвиг 8-разрядного слова вправо с вводом знакового разряда в старший разряд РОН или влево с вводом лог.0 в младший разряд регистра Q.

4.1. Изучение 8ми тестовых микропрограмм.

Микропрограмма 1.

Иллюстрирует методы загрузки данных в РОН ЦПЭ (см. табл. 4.1.1).

Таблица 4.1.1

|

Адрес памяти |

Микрокоманда |

Выполняемая функция |

|||||||

|

Адрес перехода |

Тип перехода |

Приемник результата |

Источник операнда |

Функция АЛУ |

А |

В |

D |

||

|

7 |

6 |

5 MS2 I8-I6 |

4 MS1 I2-I0 |

3 C0 I5-I3 |

2 |

1 |

0 |

||

|

0000 |

хххх |

0010 |

х011 |

х111 |

х011 |

хххх |

0000 |

0010 |

Загрузка R0 |

|

0001 |

хххх |

0010 |

х001 |

х011 |

х011 |

хххх |

0000 |

хххх |

Чтение R0 |

|

0010 |

хххх |

0010 |

х011 |

х111 |

х011 |

хххх |

0001 |

0100 |

Загрузка R1 |

|

0011 |

хххх |

0010 |

х001 |

х011 |

х011 |

хххх |

0001 |

хххх |

Чтение R1 |

|

0100 |

хххх |

0010 |

х011 |

х111 |

х011 |

хххх |

1001 |

0101 |

Загрузка R9 |

|

0101 |

0101 |

0001 |

х001 |

х011 |

х011 |

хххх |

1001 |

хххх |

Чтение R9 |

С помощью указанных микрокоманд можно загрузить в любой из 16 РОН произвольное число, меняя содержимое полей В (РОН) и D (число, которое собираемся занести в РОН). На последней микрокоманде (0101) программа зацикливается (остановка).

Рассмотрим загрузку данных в регистр Q (см. табл. 4.1.2) (изменяется приемник результата).

Таблица 4.1.2

|

Адрес памяти |

Микрокоманда |

Выполняемая функция |

|||||||

|

Адрес перехода |

Тип перехода |

Приемник результата |

Источник операнда |

Функция АЛУ |

А |

В |

D |

||

|

7 |

6 |

5 MS2 I8-I6 |

4 MS1 I2-I0 |

3 C0 I5-I3 |

2 |

1 |

0 |

||

|

1000 |

1000 |

0001 |

х000 |

х111 |

х011 |

хххх |

хххх |

0010 |

Загрузка PQ |

Микропрограмма была протестирована в лаборатории. Результаты тестирования соответствуют ожидаемым.

Микропрограмма 2.

Иллюстрирует выполнение сдвиговых операций операндов 4-разрядной и 8-разрядной длины (см. табл. 4.1.3).

Таблица 4.1.3

|

Адрес памяти |

Микрокоманда |

Выполняемая функция |

|||||||

|

Адрес перехода |

Тип перехода |

Приемник результата |

Источник операнда |

Функция АЛУ |

А |

В |

D |

||

|

7 |

6 |

5 MS2 I8-I6 |

4 MS1 I2-I0 |

3 C0 I5-I3 |

2 |

1 |

0 |

||

|

0000 |

хххх |

0010 |

х011 |

х111 |

х011 |

хххх |

0000 |

0010 |

Загрузка R0 |

|

0001 |

хххх |

0011 |

0111 |

1011 |

х011 |

хххх |

0000 |

хххх |

Сдвиг R0 влево циклический |

|

0010 |

хххх |

0011 |

0101 |

1011 |

х011 |

хххх |

0000 |

хххх |

Сдвиг R0 вправо |

|

0011 |

хххх |

0010 |

х000 |

х010 |

Х100 |

хххх |

хххх |

хххх |

Обнуление Q |

|

0100 |

хххх |

0011 |

1110 |

0011 |

х011 |

хххх |

0000 |

хххх |

Циклический сдвиг двойной длины влево |

|

0101 |

хххх |

0011 |

1100 |

0011 |

х011 |

хххх |

0000 |

хххх |

Циклический сдвиг двойной длины вправо |

|

0110 |

0110 |

0001 |

х001 |

х011 |

х011 |

хххх |

хххх |

хххх |

Пустая операция |

При помощи использования микрокоманд (1, 2, 3, 5 и 6), в которых реализуется переход по адресу, формируемому клавишным регистром адреса, можно выполнять операции, определяемые операционным полем микрокоманды, произвольное число раз. Тип сдвиговых операций задается разрядами MS2 и MS1 микрокоманды.

Рассмотрим пример выполнения программы(см табл. 4.1.3.1).

Таблица 4.1.3.1

|

АДРЕС |

ДАННЫЕ |

Комментарий |

|

0000 |

0010 |

Загрузка R0 |

|

0001 |

0010 |

Циклический сдвиг влево, на клавишном регистре адреса 0001 |

|

0001 |

0100 |

|

|

0001 |

1000 |

|

|

0001 |

0001 |

|

|

0001 |

0010 |

|

|

0001 |

0100 |

На клавишном регистре адреса 0010 |

|

0010 |

1000 |

Циклический сдвиг вправо, при этом сдвиг влево виден на этом такте работы. На клавишном регистре адреса 0010 |

|

0010 |

0100 |

|

|

0010 |

0010 |

На клавишном регистре адреса 0011 |

|

0011 |

0000 |

Обнуление Q, теперь будим сдвигать двойное слово 0001 0000 |

|

0100 |

0001 |

Индикатор ДАННЫЕ указывает значение регистра РОН0, двойное слово: 0001 000. Переход осуществляется по клавишному регистру адреса, адрес 0100 |

|

0100 |

0010 |

0010 0000 |

|

0100 |

0100 |

0100 0000 |

|

0100 |

1000 |

1000 0000 |

|

0100 |

0000 |

0000 0001 |

|

Таблица 4.1.3.1 (окончание). |

||

|

0100 |

0000 |

0000 0010 |

|

0100 |

0000 |

0000 0100 |

|

0100 |

0000 |

0000 1000 |

|

0100 |

0001 |

на клавишном регистре адреса значение 0101 |

|

0101 |

0010 |

Слово 0010 0000, выполняется сдвиг вправо, но на индикаторах всё ещё отображается сдвиг влево |

|

0101 |

0001 |

0001 0000 |

|

0101 |

0000 |

0000 1000 |

|

0101 |

0000 |

0000 0100 |

|

0101 |

0000 |

0000 0010 |

|

0101 |

0000 |

0000 0001 |

|

0101 |

1000 |

1000 0000 |

|

0101 |

0100 |

0100 0000, переход на адрес 0110 |

|

0110 |

0010 |

Пустая операция, но отображается сдвиг |

|

0110 |

0010 |

Пустая операция |

Изменение флагов при сдвиге двойного слова.

Флаги переполнения и переноса из старшего разряда установлены при сдвигах всегда. Флаг знака результата устанавливается один раз за 8 тактов работы, когда единица достигает старшего (знакового) разряда РОНа. Флаг нулевого результата устанавливается в единицу в течение половины цикла сдвига, так как в слове содержится только одна единица, время "прохождения" которой по 4-разрядному регистру РОН или Q составляет 4 такта.

Отображение результата сдвига происходит на следующем такте работы, так как сдвиги осуществляются не в АЛУ на спаде синхросигнала. Операция происходит, но результат отображается только на следующем такте.

Рассмотрим микропрограмму, демонстрирующую выполнение арифметического сдвига 8-разрядной длины вправо, влево, 4-разрядного сдвига с вводом лог. 0 в старшие (при сдвиге вправо) или младшие (при сдвиге влево) разряды РОН и регистра Q.

Таблица 4.1.4

|

Адрес памяти |

Микрокоманда |

Выполняемая функция |

|||||||

|

Адрес перехода |

Тип перехода |

Приемник результата |

Источник операнда |

Функция АЛУ |

А |

В |

D |

||

|

7 |

6 |

5 MS2 I8-I6 |

4 MS1 I2-I0 |

3 C0 I5-I3 |

2 |

1 |

0 |

||

|

0000 |

хххх |

0010 |

х011 |

х111 |

х011 |

хххх |

0000 |

0010 |

Загрузка R0 |

|

0001 |

хххх |

0011 |

0111 |

0011 |

х011 |

хххх |

0000 |

хххх |

Сдвиг R0 влево с вводом лог. 0 в младшие разряды |

|

0010 |

хххх |

0011 |

0101 |

0011 |

х011 |

хххх |

0000 |

хххх |

Сдвиг R0 вправо с вводом лог. 0 в старшие разряды |

|

0011 |

хххх |

0010 |

х000 |

х010 |

х100 |

хххх |

хххх |

хххх |

Обнуление Q |

|

0100 |

хххх |

0011 |

1110 |

1011 |

х011 |

хххх |

0000 |

хххх |

Арифметический сдвиг двойной длины влево |

|

0101 |

хххх |

0011 |

1100 |

1011 |

х011 |

хххх |

0000 |

хххх |

Арифметический сдвиг двойной длины вправо |

|

0110 |

0110 |

0001 |

х001 |

х011 |

х011 |

хххх |

хххх |

хххх |

Пустая операция |

Выполнение программы аналогично, результаты отражают конкретно выполняемый сдвиг, правила выполнения арифметических сдвигов см. выше.

В МПК1804ВС1 при сдвиговых операциях выдвигаемый бит не фиксируется. Значение выдвигаемого бита обычно используется при реализации

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.