S(2*N1-3 downto 0) <=

S_abs when '0',

not( S_abs ) when '1';

END COD_CONVERT_arch;

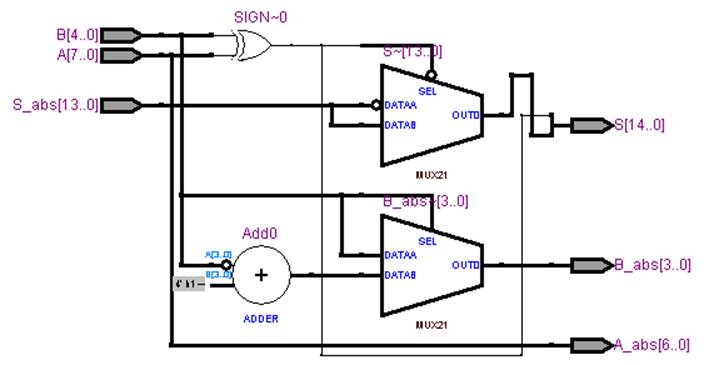

рис 2.9. Синтезированная схема блока COD_CONVERT

в RTL Viewer.

Блок COD_CONVERT представляет собой комбинационное устройство, которое в зависимости от знаков операнда и результатов выделят модули для передачи их на умножитель и преобразует результат в заданный код в зависимости от знака результата.

3. Исследование мегафункции LPM_MULT.

3.1. Исследование неконвейеризированного умножителя LPM_MULT.

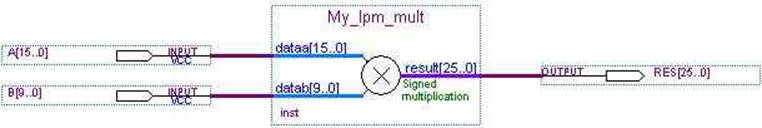

Рис.3.1. Исследование

умножителя LPM_MULT.

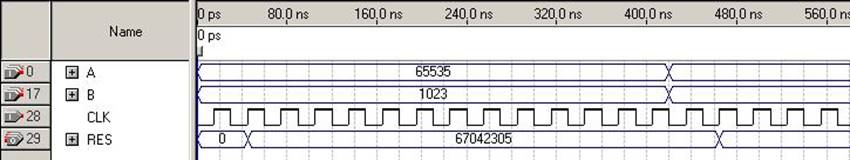

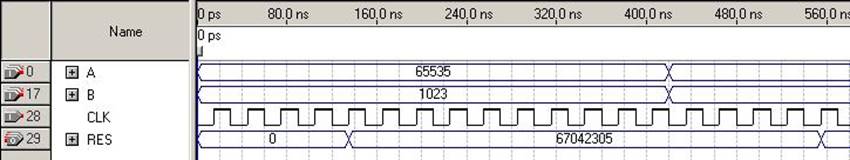

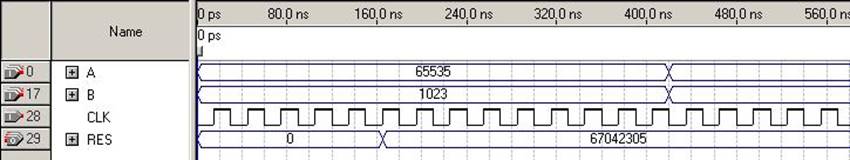

Проверку правильности функционирования умножителя показывают следующие временные диаграммы.

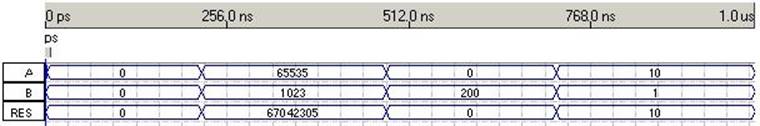

Без знаковое умножение.

Рис.3.2. Диаграмма работы без

знакового умножителя.

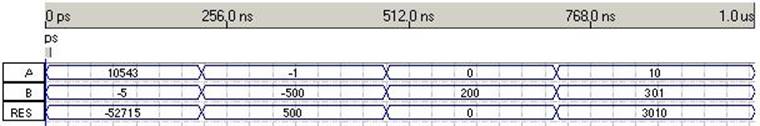

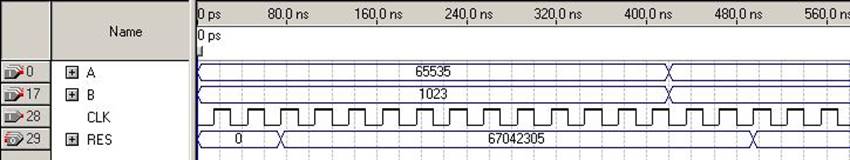

Умножение чисел со знаком.

Рис.3.3. Диаграмма работы

знакового умножителя.

Умножитель функционирует правильно, все знаковые соотношения соблюдаются. При работе с числами со знаком вычисления ведутся в дополнительных кодах.

На ПЛИС умножитель может быть реализован с использованием логических элементов и с использованием встроенных умножителей. Сравнение этих двух возможных реализаций приведено в таблице.

Таблица 3.1.1

|

Реализация на логических ячейках |

Реализация на встроенных умножителях |

|

|

Аппаратные затраты |

206 lut |

1 DSP 18x18 |

|

tpdmax для выходной шины |

27.107 ns |

19.785 ns |

|

tpdmin для выходной шины |

21.927 ns |

18.312 ns |

В редакторе назначений для выходной шины предъявим требование к максимальной задержке. Параметр tpd Requirement задан равным минимальному значению tpd из предыдущей таблицы.

Таблица 3.1.2

|

Реализация на логических ячейках |

Реализация на встроенных умножителях |

|

|

tpdmax для выходной шины |

19.424 ns |

15.812 ns |

|

tpdmin для выходной шины |

18.393 ns |

15.183 ns |

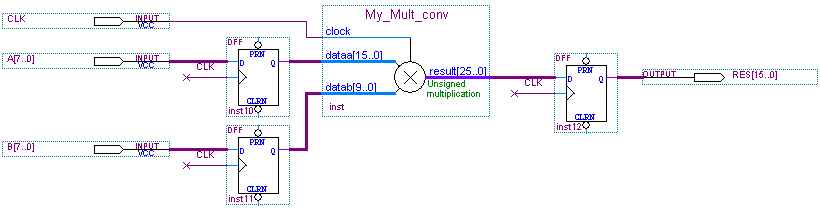

3.2. Исследование конвейеризированного умножителя LPM_MULT.

Рис.3.2. Исследование

конвейеризированного умножителя LPM_MULT.

D-триггеры необходимы для измерения тактовой частоты работы, так как она измеряется относительно задержек на триггерах.

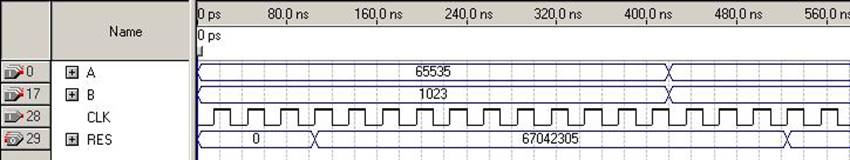

Временные диаграммы работы конвейеризированных умножителей.

рис.3.2.1. 0 этапов конвейера.

рис.3.2.2. 1 этап конвейера.

рис.3.2.3. 2 этапа конвейера.

рис.3.2.4. 3 этапа конвейера.

Рис.3.2.5. 4 этапа конвейера.

Увеличение числа этапов конвейера вносит задержку появления результата на выходной шине результата. Один этап вносит задержку на один такт частоты. (В данном на диаграммах еще один такт задержки появляется от регистров на входах и выходе умножителя).

Оцениваются аппаратурные затраты и производительность для разного числа этапов конвейера и реализации с помощью логических ячеек.

Таблица 3.2. Реализация умножителя на логических элементах

|

Этапы конвейера |

0 |

1 |

2 |

3 |

4 |

|

Аппаратные затраты |

231 lut |

124 lut 96 reg |

124 lut 125 reg |

124 lut 181 reg |

124 lut 301 reg |

|

Наименьшее значение Fmax |

81.65 MHz |

133.26 MHz |

127.40 MHz |

119.22 MHz |

208.46 MHz |

|

Наибольшее значение Fmax |

102.40 MHz |

154.68 MHz |

158.93 MHz |

187.06 MHz |

246.73 MHz |

При увеличении числа этапов конвейера в умножителе, тактовая частота его работы увеличивается, но при этом возрастают и аппаратурные затраты.

4. Анализ результатов работы. Сравнение вариантов реализации умножителей.

Сопоставляя возможные реализации умножителей можно сделать следующие выводы.

Если сравнивать последовательные умножители с матричными, то если критерием оценки считать аппаратные затраты, то здесь преимущество у последовательных умножителей, так например, для реализации последовательно умножителя чисел разрядности 8 необходимо 38 ячеек, то для матричного умножителя чисел такой же разрядности на логических элементах требуется 107 логических ячеек. Таким образом, если нужно не очень большое быстродействие, то можно использовать последовательные умножители.

Если сравнивать реализацию матричных умножителей на логических элементах и на встроенных умножителях, то если на используемой микросхеме они есть как отдельные блоки, то лучше использовать их, так как при умножении чисел большой разрядности получаются довольно большие аппаратные затраты.

Ковейеризованный умножитель производительнее нековейеризованного, но при этом увеличение тактовых частот работы сопряжено с затратой аппаратных ресурсов.

Как итог, можно сделать вывод, что выбор реализации умножителя зависит от решаемой задачи — необходимой для ее решения производительности и доступных аппаратных ресурсов.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.