Порты с 16 по 19 (выходы дешифратора 1-4) служат для подключения входов разрешения регистров. 19 адрес в принципиальной схеме не используется, но для удобства он присутствует в таблице, так как А0 и А1 на следующем адресе равны нулю, что позволяет применить последующие адреса (выводы микросхемы) для управления интерфейсным блоком на основе КР580ВВ55А.

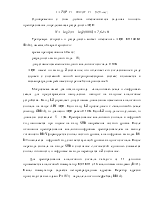

Таблица 2 –Адресное пространство для внешних устройств

|

Подключаемое внешнее устройство |

Адрес |

Разряды адресной шины |

||||||||

|

<10> |

<16> |

А7 |

А6 |

А5 |

А4 |

А3 |

А2 |

А1 |

А0 |

|

|

Индикация (RG1) DD10 |

16 |

10 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

Индикация (RG2) DD11 |

17 |

11 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

|

АЦП (RG3) DD12 |

18 |

12 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

- |

19 |

13 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

|

Порт А DD9 |

20 |

14 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

|

Порт В DD9 |

21 |

15 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

|

Порт С DD9 |

22 |

16 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

|

Регистр шин DD9 |

23 |

17 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

|

– |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

|

– |

31 |

1F |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1.6 Блок ввода аналоговых данных

Задача блока ввода аналоговых данных (БВВАД) согласно техническому заданию - обеспечить периодическое преобразование входных аналоговых данных в цифровой код, а также передачу его в микропроцессорный блок.

Целесообразным является построение БВВАД по последовательной схеме, состоящей из аналогового коммутатора (АК) (DA1) и аналого-цифрового преобразователя (АЦП). Структура БВВАД и его интерфейса зависит от типа АЦП и АК, поэтому сначала необходимо выбрать АЦП.

Согласно техническому заданию, максимально допустимое время преобразования в АЦП должно быть не более:

t < T/(P+1) = 990/(11+1) = 82,5 мкс;

Одновременно с этим должна обеспечиваться заданная точность преобразования, определяющая разрядность АЦП:

N > – log2 d = – log2(0.005) = 7,64 » 8;

Требуемую скорость и разрядность может обеспечить АЦП К1113ПВ1 (DA3), имеющий характеристики:

- время преобразования 30 мкс;

- разрядность выходного кода – 10;

- допустимое изменение входного аналогового сигнала 0-10В

АЦП имеет по выходу Z-состояние, что облегчает его согласование в ряде случаев с системной шиной микропроцессорных систем; включается в восьмиразрядном режиме с внутренней синхронизацией.

Микросхема имеет два общих провода – «аналоговая» земля и «цифровая» земля для предотвращения импульсных наводок на входные аналоговые устройства. Вход LZ управляет допустимым диапазоном изменения аналогового сигнала на входе AIN АЦП. Если вход LZ присоединен к «аналоговой» земле (выводу GRDA), то диапазон АЦП равен 0-10В. Если LZ никуда не подключен, то диапазон составляет -5 - +5В. Преобразование аналогового сигнала в цифровой код начинается при подаче на вход STR напряжения низкого уровня. После окончания преобразования аналогово-цифровым преобразователем на выводе готовности RDY формируется сигнал низкого уровня, а на цифровых выходах D0-D9 появляется цифровой код, соответствующий уровню входного сигнала. После перехода сигнала на входе STR в состояние «логической единицы» снимается сигнал готовности, и цифровые выходы переводятся в Z-состояние.

Для преобразования аналогового сигнала каждого из 11 датчиков применяется аналоговый коммутатор К591КН1 с 16 аналоговыми входами (DА1). Канал коммутатора задаётся четырёхразрядным адресом. Перебор адресов производится выходами PА(0-3) параллельного интерфейса (DD14).

Для связи АК с АЦП применяется операционный усилитель К140УД6 (DA2). Так как напряжение аналогового сигнала (5В) меньше допустимого входного напряжения АЦП (10 В), для увеличения точности преобразования, этот операционный усилитель включается в режиме прямого усиления. Для этого производится расчет элементов обвязки ОУ. R6 стандартный для микросхем этого типа и он равен 10кОм (предназначен для компенсации дрейфа нуля). Коэффициент усиления по напряжению должен быть равен 10В/6В=1.67, он находится по формуле K=1+R4/R5, R4 выбирается равным 4кОм (по характеристикам ОУ), тогда R5 = 6.1кОм.

1.7 Блок отображения информации и блок вывода результата

Для отображения результата вычислений применяются семисегментные знакосинтезирующие индикаторы АЛС324А (HG1 – HG3). Количество разрядов отображаемого десятичного числа определяется разрядностью данных. Так при разрядности данных равной 8 количество индикаторов должно быть равным 3, так как семиразрядное число может принимать значения 0 – 28 = 256. Для преобразования двоичного кода в код индикатора применяются дешифраторы К514ИД1 (DD13 – DD15). Код результата записывается в буферные регистры (DD10, DD11), сохраняющие код до следующей записи. В регистры записывается двоично-десятичный код.

Для преобразования результата из двоичного цифрового вида в аналоговую форму применяем цифро-аналоговый преобразователь КР572ПА1А (DА4). В цепь ЦАП входит операционный усилитель, который и организует связь с ЦАП. Входы ЦАП D2 – D9 подключаются к выходам Q0 – Q7 буферного регистра

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.