Микросхема КР537РУ10 имеет совмещенные выходы и сигнал управления состоянием выхода CEO. В разрабатываемой МПС микросхема К537РУ10 подключается непосредственно к шинам МПС(см. приложение 2). При последовательном обращении используется режим обращения с постоянной выборкой, возможный благодаря асинхронности выбранной БИС ОЗУ. Иначе, сигнал CS(A15) изменяется, вообще говоря, не в каждом цикле, а при первом обращении в случае чтения/записи нескольких ячеек. По сигналу WR осуществляется запись информации в микросхему. Сигнал RD управляет входом разрешения выдачи.

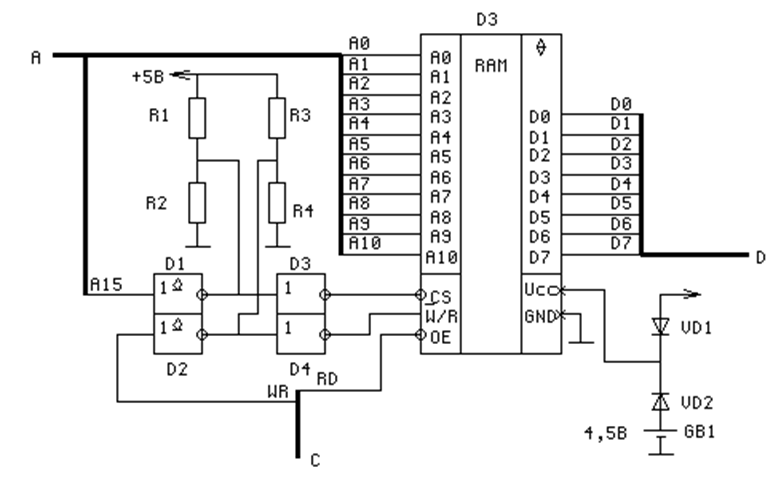

Принципиальная схема модуля NVRAM, построенная в соответствии

с [6], приведена на рис. 2.67. БИС ОЗУ

обозначена как D3. При отказе основного источника питания происходит переход на

резервный(батарею), что обеспечивается диодами VD1 и VD2. На входах CS и W/R

микросхемы установлены элементы, позволяющие избежать искажения информации,

записанной в ОЗУ, при работе от батареи. Каждый вход отделен от шины управления

цепочкой из двух инверторов, ТТЛ-ОК(D1, D2) и КМОП(D3, D4), способных работать

при пониженном напряжении питания. Элемент с ОК используется для получения

входных уровней КМОП. На входе инвертора КМОП имеется резистор, соединяющий его

с общей шиной. Питание инверторов КМОП осуществляется по той же шине питания,

что и БИС ОЗУ. На входе каждого инвертора КМОП имеется резистор, соединяющий

его с общей шиной. Т.о., при отключении основного источника питания на входе

инвертора устанавливается логический «0», на выходе--логическая «1», и БИС ОЗУ

переходит в режим хранения, отключаясь от внешних цепей.

Рис. 2.7. Функциональная схема модуля энергонезависимого ОЗУ

Произведем расчет элементов схемы блокировки входных цепей управления БИС ОЗУ. Выберем в качестве D1 микросхему КР1533ЛН2 (6 инверторов с открытым коллекторным выходом) с параметрами[4]: IOL£8 мА; ICC£10 мА; CLlim=200 пФ; tP£34 нс. Выберем в качестве D2 микросхему КР1554ЛН1 (6 инверторов) с параметрами: UOH£0.7UCC; UOL³0.3UCC; CPD£30пФ; CLlim=500 пФ; tP£10 нс. В соответствии с рекомендациями [6] резистор R2, соединяющий вход инвертора КМОП с общей шиной, имеет номинал 10кОм. Минимальный номинал резистора R1 определяется предельно допустимым выходным током инвертора ТТЛ:

R1min=(UCCmax-UOLmin)/IOLmax=5.5/(8*10-3)»690 Ом.

Резисторы R1, R2 образуют делитель. Если выход инвертора ТТЛ находится в состоянии логической «1», его выходной транзистор закрыт и его влиянием, как и влиянием высокоомного КМОП-входа, можно пренебречь. Рассчитаем R1max из условия сохранения требуемого входного уровня КМОП:

UIHCMOS=UCC*R2/(R1max+R2),

R1max=R2*(UCC-UIHCMOS)/UIHCMOS=R2*0.3*UCC/(0.7*UCC)»0.4*R2=4кОм, где UIHCMOS-минимальный допустимый уровень входного напряжения логической «1» на входе инвертора КМОП. Для обеспечения помехоустойчивости выберем R1=1кОм.

Произведем расчет и выбор диодов VD1 и VD2. Для этого необходимо определить ток потребления питаемых через них микросхем, т.е. D2 и D3. В соответствии с [4], для микросхем серии КР1554, ток потребления в динамическом режиме состоит из трех составляющих: тока потребления в статическом режиме, тока перезарядки нагрузочной емкости CL, тока перезарядки внутренней емкости и сквозных токов. Динамическая мощность потребления PD(мкВт) определяется по формуле:

PD=CPD*UCC*FI+N*(CL*UCC*F0), где FI-входная частота (МГц), FO-выходная частота (МГц), N-количество переключающихся выходов. Поскольку в ОМЭВМ КР1816ВЕ31 обращение к памяти данных происходит 1 раз за машинный цикл, FI=FO=fBQ/12=F=833 кГц. Тогда динамический ток потребления составит

ICCO=F*(CPD+2*CL)=0.833*(30+2*8)=38мкА.

Общий ток потребления D2 и D3

Icc=Icc(D2)+Icco(D2)+Icc(D3)=70*10-3+78*10-6»71мА.

Из условия способности диода пропустить прямой ток, равный Icc, выберем в качестве VD1, VD2 диоды КД103А с максимальным прямым током 100мА[10]. Выберем напряжение резервного источника питания 4.5В, что позволит реализовать его на стандартных гальванических элементах.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.